# A new programmable low noise all digital phase-locked loop architecture

by

Justin L. Gaither

## A thesis submitted to the graduate faculty in partial fulfillment of the requirements for the degree of MASTER OF SCIENCE

Major: Computer Engineering

Program of Study Committee: Marwan Hassoun, Major Professor Doug Jacobson Robert Weber Gurpur Prabhu

Iowa State University

Ames, Iowa

2005

Copyright © Justin L. Gaither, 2005. All rights reserved.

Graduate Collage Iowa State University

This is to certify that the master's thesis of Justin L. Gaither has met the thesis requirements of Iowa State University

Signatures have been redacted for privacy

# **Table of Contents**

| List of Figuresv                                                  |

|-------------------------------------------------------------------|

| List of Tablesvii                                                 |

| Acknowledgementsviii                                              |

| Abstractix                                                        |

| Chapter 1 Introduction                                            |

| 1.1 Introduction1                                                 |

| 1.2 Overview of Various PLL Architectures and their Applications1 |

| 1.2.1 Classic Digital PLL3                                        |

| 1.2.2 All-Digital PLL4                                            |

| 1.2.3 Software PLL5                                               |

| 1.3 Overview of Various PLL Components5                           |

| 1.3.1 Digital phase detectors5                                    |

| 1.3.2 Charge Pumps and Loop Filters8                              |

| 1.3.3 Controlled Oscillators9                                     |

| 1.4 Thesis contribution10                                         |

| 1.4.1 Architecture and Design10                                   |

| 1.5 Analysis of implemented loop parameters12                     |

| 1.5.1 DAC Resolution and Sample Rate12                            |

| 1.5.2 Loop Filter Gain13                                          |

| 1.6 Conclusion13                                                  |

| Chapter 2 Implementation                                          |

| 2.1 Introduction14                                                |

| 2.2 Design                                                        |

| 2.2.1 Phase Detector                                              |

| 2.2.2 Loop Filter17                                               |

| 2.2.3 SPI – Serial Peripheral Interface19                         |

| 2.2.4 VCO Divider (vcodiv)20                                      |

| 2.2.5 Digital to Analog Converter                                 |

| 2.2.6 Voltage Controlled Crystal Oscillator2    | 3 |

|-------------------------------------------------|---|

| 2.2.7 ChipScope Pro2                            | 4 |

| 2.3 FPGA compile and P&R2                       | 7 |

| 2.4 Conclusion                                  | 7 |

| Chapter 3 Measured Results                      | 9 |

| 3.1 Introduction                                | 9 |

| 3.2 Measurement Setup                           | 9 |

| 3.3 Labview Automation                          | 0 |

| 3.4 Jitter Transfer                             | 6 |

| 3.5 Jitter Generation4                          | 3 |

| 3.6 Frequency Step Response4                    | 8 |

| 3.7 Data Recovery Jitter Tolerance              | 1 |

| 3.8 Comparison to Analytical Analysis           | 2 |

| 3.9 Conclusion                                  | 3 |

| Chapter 4 Conclusion                            | 4 |

| 4.1 Future Work                                 | 5 |

| Appendix A                                      | 6 |

| 4.2 Introduction                                | 6 |

| 4.3 Design Top-Level module : fpga_top.v5       | 6 |

| 4.4 Accumulating Phase Detector Module : pd.v6  | 0 |

| 4.5 Loop Filter Module : lp.v6                  | 4 |

| 4.6 Serial Peripheral Interface module : spi.v6 | 7 |

| 4.7 VCO divider Module : vcodiv.v               | 9 |

| References                                      | 2 |

# **List of Figures**

| Figure 1 : Simple Phase-Locked Loop Diagram                  | 2   |

|--------------------------------------------------------------|-----|

| Figure 2 : Conceptual diagram of Linear PLL                  | 2   |

| Figure 3 : Digital PLL Diagram                               | 4   |

| Figure 4 : All-Digital PLL Diagram                           | 4   |

| Figure 5 : XOR Based Phase Detector                          | 5   |

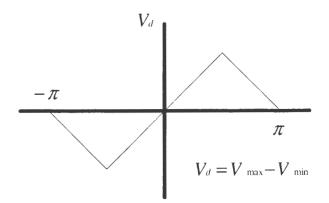

| Figure 6 : XOR PD Response                                   | 6   |

| Figure 7 : Phase-Frequency Detector                          | 7   |

| Figure 8 : PFD Response                                      | 7   |

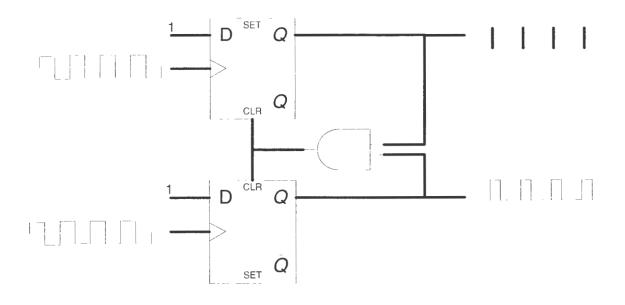

| Figure 9 : Alexander (Bang-Bang) Phase Detector              | 8   |

| Figure 10 : Bang-Bang PD Response                            | 8   |

| Figure 11 : Example Charge Pump and Loop Filter              | . 9 |

| Figure 12 : Simplified Design Architecture                   | 11  |

| Figure 13 : Simplified System Level Diagram                  | 15  |

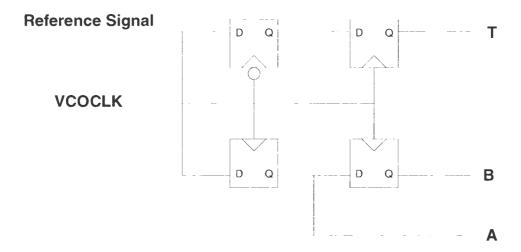

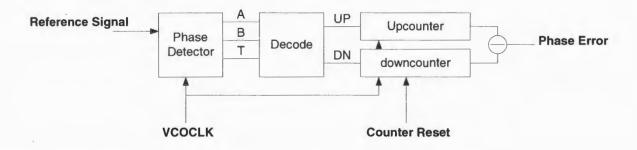

| Figure 14 : Accumulating Bang-Bang Phase Detector            | 15  |

| Figure 15 : Accumulating Phase Detector Input Output Diagram | 16  |

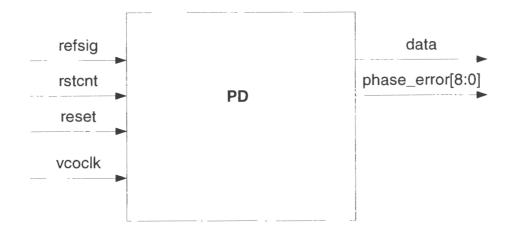

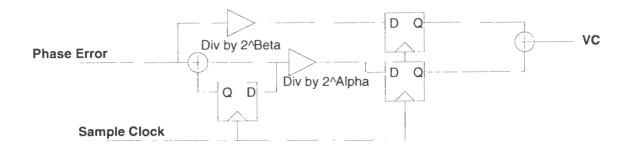

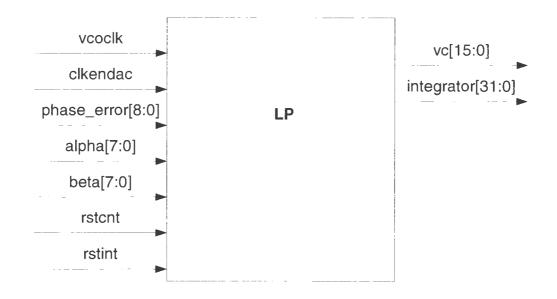

| Figure 16 : Digital Loop Filter Implementation               | 17  |

| Figure 17 : Loop Filter Input Output Diagram                 | 18  |

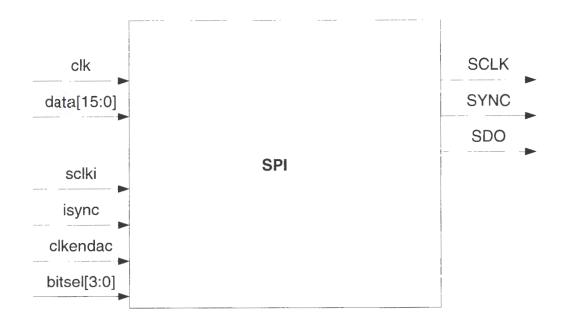

| Figure 18 : SPI Input and Output Diagram                     | 19  |

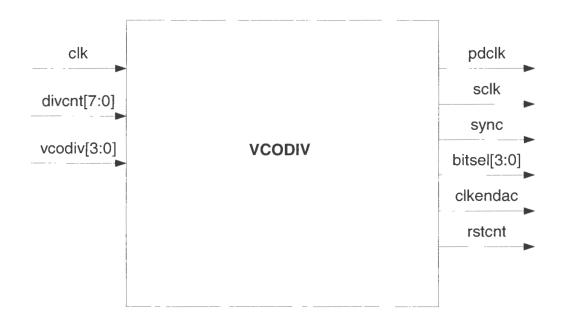

| Figure 19 : VCODIV Input/Output Diagram                      | 20  |

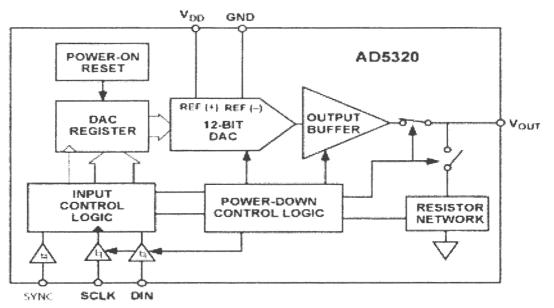

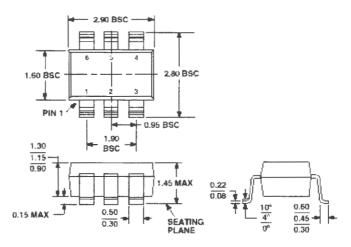

| Figure 20 : AD5320 Diagram                                   | 22  |

| Figure 21 : AD5320 Package Diagram                           | 22  |

| Figure 22 : ChipScope Pro Screen Capture                     | 25  |

| Figure 23 : Detailed Diagram of FPGA                         | 26  |

| Figure 24 : Picture of MK20XFP Board                         | 28  |

| Figure 25 : Jitter Transfer3.vi Front Panel                  | 31  |

| Figure 26 : Jitter Transfer3.vi Block diagram                | 32  |

| Figure 27 : Multiple_jitter_transfer3.vi Front Panel         | 34  |

| Figure 28 : Multiple_jitter_transfer3.vi Block Diagram       | 35  |

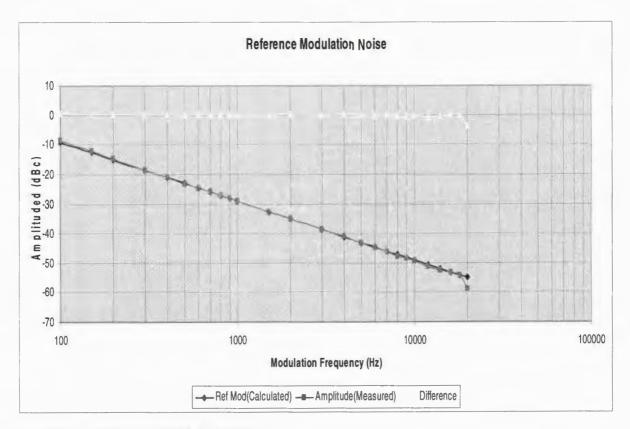

| Figure 29 : Fixed Control Voltage Noise Plot                       | 36 |

|--------------------------------------------------------------------|----|

| Figure 30 : Reference Modulation Plot                              | 37 |

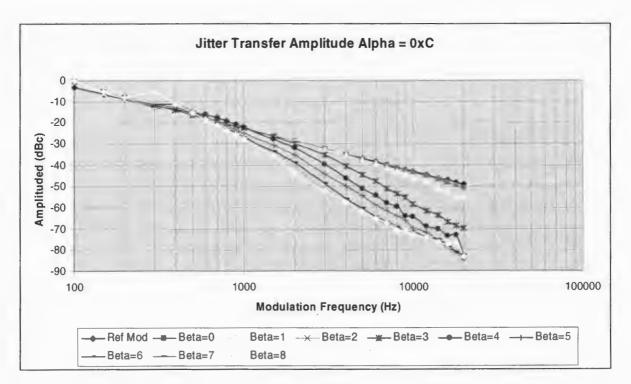

| Figure 31 : Jitter Transfer Amplitude Alpha=0xC                    | 38 |

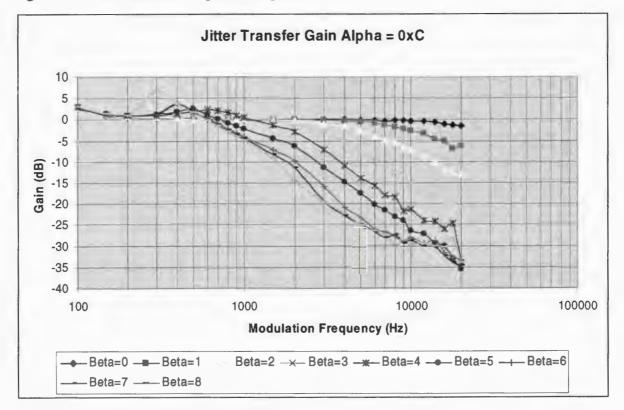

| Figure 32 : Jitter Transfer Gain Alpha=0xC                         | 38 |

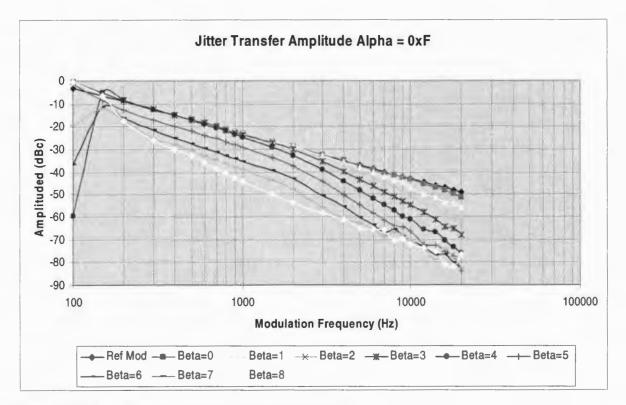

| Figure 33 : Jitter Transfer Amplitude Alpha=0xF                    | 39 |

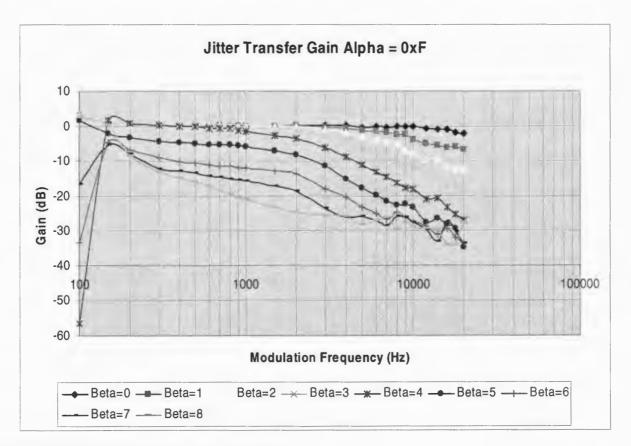

| Figure 34 : Jitter Transfer Gain Alpha=0xF                         | 40 |

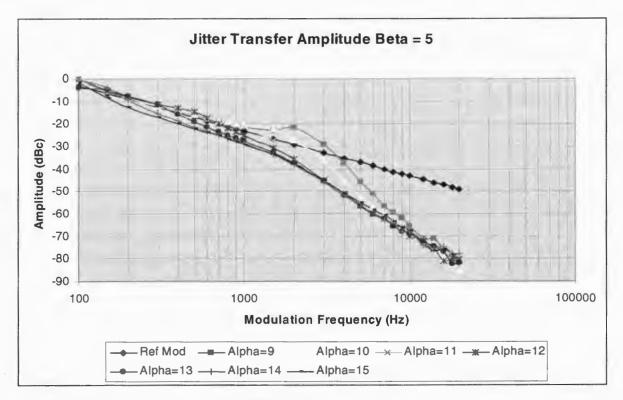

| Figure 35 : Jitter Transfer Amplitude Beta=5                       | 41 |

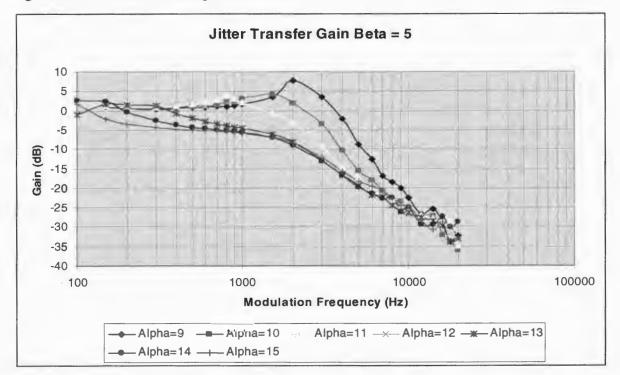

| Figure 36 : Jitter Transfer Gain Beta=5                            | 41 |

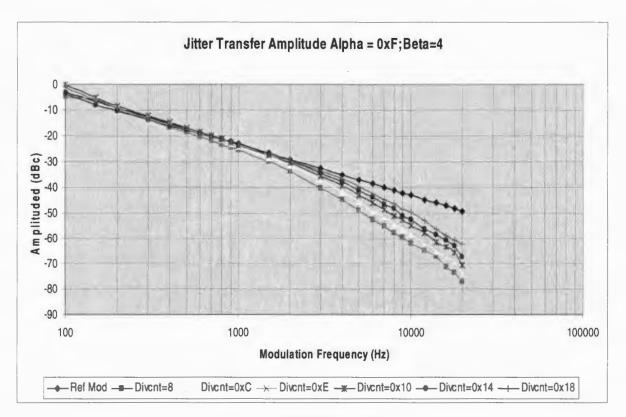

| Figure 37 : Jitter Transfer Amplitude Alpha=0xF;Beta=4             | 42 |

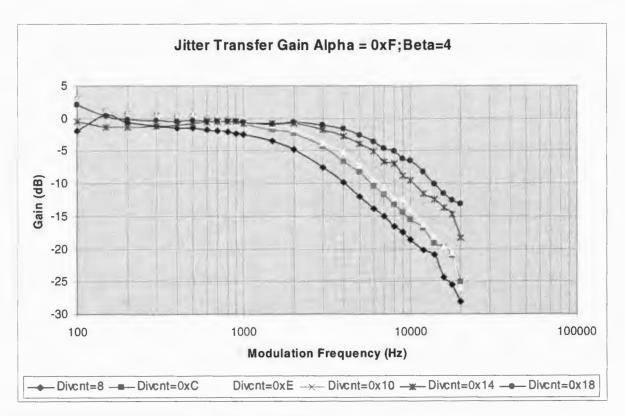

| Figure 38 : Jitter Transfer Gain Alpha=0xF;Beta=4                  | 43 |

| Figure 39 : Phase Noise Measurement Reference                      | 44 |

| Figure 40 : Phase Noise Measurement Fixed DAC value                | 45 |

| Figure 41 : Phase Noise Measurement Alpha=3;Beta=0                 | 46 |

| Figure 42 : Phase Noise Measurement Alpha=0xF;Beta=5               | 47 |

| Figure 43 : 1000Hz Frequency Step Response Alpha=6;Beta=3          | 48 |

| Figure 44 : 1000Hz Frequency Step Response Alpha=6;Beta=2          | 49 |

| Figure 45 : Negative 1000Hz Frequency Step Response Alpha=9;Beta=5 | 50 |

| Figure 46 : Positive 1000Hz Frequency Step Response Alpha=9;Beta=5 | 51 |

| Figure 47 : Jitter Tolerance Plots                                 | 52 |

# **List of Tables**

| Table 1 : BBPD decode table                                    | 16 |

|----------------------------------------------------------------|----|

| Table 2 : Accumulating Phase Detector Input Output Description | 17 |

| Table 3 : Loop filter Input Output Description                 | 18 |

| Table 4 : SPI Input and Output Description                     | 20 |

| Table 5 : VCODIV Input and Output Description                  | 21 |

| Table 6 : VCXO specifications                                  | 23 |

| Table 7 : Programmable settings and monitors                   | 24 |

| Table 8 : Equipment List for Test Setup #1                     | 29 |

| Table 9 : Equipment List for Test Setup #2                     | 30 |

| Table 10 : Comparison of minimum Beta                          | 53 |

# Acknowledgements

I wish to give special thanks to Brian Brunn for his assistance and mentorship while I worked on this project, as well as Xilinx, Inc for supporting the development, design and testing.

I would also like to recognize my wife Patricia and my children Brittany and Hanna for their sacrifices and encouragement while I worked to complete my degree.

## Abstract

In the electronics industry today almost without exception there are phase-locked loops (PLL) implemented within each system and often within each integrated circuit (IC). In fact, most PLL's are implemented monolithically within ICs without any or with very few external components. Additionally, most are implemented as Analog PLL's utilizing only a digital phase detector. This is also evident in the majority of recent publications which focus on PLL structures with on-chip voltage controlled oscillators using charge pumps and ring or LC oscillators. However, the problem with most on-chip VCO's is that they are far noisier than the external crystal types. The noise in the integrated oscillators forces designers to use larger loop bandwidths than would be required with less noisy VCO's; subsequently they have poor noise filtering capabilities. Additionally, analog PLL's are usually fixed in nature. Loop components such as charge-pumps and loop filters are implemented as analog components with little or no flexibility. The focus of this thesis is the design and implementation of a very low cost, low noise Programmable All Digital PLL (ADPLL) which utilizes a low cost digital to analog converter (DAC), a voltage controlled crystal oscillator (VCXO), and a field programmable gate array (FPGA). The use of FPGA technology for digital design implementation is universal in the industry and provides benefits far beyond the implementation of ADPLL's. In fact, in almost every system today, an FPGA already exists. Therefore, the inclusion of a DPLL within existing system components would be at little or no cost. The implementation of the PLL digitally not only allows us to implement it within an FPGA, but also allows us to adapt and configure the PLL for many applications and tune it for best performance. Digital circuits also have increased noise margin and are not affected by the same noise issues associated with Analog PLL's such as temperature, voltage and noise coupled from other signals or circuits. The DPLL developed is flexible and can be configured to operate as a clock and data recovery circuit (CDR), clock multiplier, clock synthesizer, or noise filtering PLL. Using an external VCXO provides a very low noise basis for the PLL and such that we can implement very low bandwidths without sacrificing the quality of its output. In this thesis we will present the theory, architecture, design, hardware and implementation of the ADPLL in addition to the results of the testing of the prototype ADPLL that was built.

## **Chapter 1 Introduction**

### **1.1 Introduction**

This chapter provides preliminary information and background on Phased-Locked Loop (PLL) design, architectures, and components. Furthermore the specific implementation that this thesis contributes will be introduced. Theoretical analysis of the implementation will also be discussed.

### 1.2 Overview of Various PLL Architectures and their Applications

Phase-Locked Loops are used in many applications, and are as wide spread as any other circuit type[1]. In the earliest history they were used to sync the horizontal and vertical sweeps in television[1]. Today, they are used as clock multipliers in high performance microprocessors such as Intel Pentium 4. As such their benefits and properties have been studied and documented in countless journal papers, books, and articles. In fact there exists so much information about PLL's it can be overwhelming and difficult to isolate the specific information a researcher may be searching.

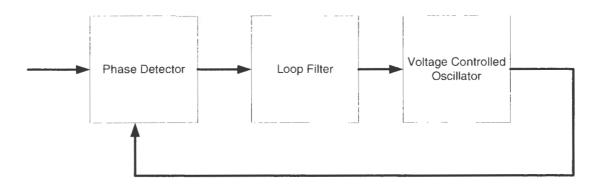

A basic Phase-Locked Loop consists of three basic components, a phase detector, a loop filter, and a voltage or current controlled oscillator.

1. The phase detector can be considered the brain. It makes the decisions about the behavior of the loop. Often it is a non-linear device whose output contains the phase or frequency difference between its reference and the controlled oscillator.

2. The loop filter can be considered the muscle. It controls how much impact the decision of the brain or phase detector has on the controlled oscillator. Its properties are what keep the loop stable and affect the performance.

3. The voltage or current controlled oscillator is the heart. It is central to the loop and its periodic nature keeps the loop ticking. The frequency of its output is dependent upon a much lower frequency and lower amplitude signal.

Figure 1 : Simple Phase-Locked Loop Diagram

Figure 1 shows how these components connect in a feedback architecture to create a simple phase-locked loop. However, as with any feedback architecture there must exist a balance within the loop to maintain stability and performance. The classic analysis of the PLL requires certain assumptions be made such as linearity[1]. Both the phase detector and the controlled oscillator have non-linear operating points. Luckily they also have linear or near-linear operating points when differences in phase are small. This allows analysis to be performed in the frequency domain using Laplace transformations.

Figure 2 : Conceptual diagram of Linear PLL

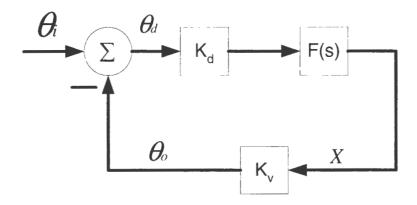

Figure 2 shows a conceptual diagram of a linear PLL[1]. This linear PLL is described in the frequency domain by the equation (1).

$$T(s) = \frac{\theta_{a}(s)}{\theta_{b}(s)} = \frac{s}{s + K_{d}K_{v}F(s)}$$

(1)

The earliest PLL's, such as the one shown in Figure 1, were completely analog. The phase detectors where mixers, the loop filters consisted of active amplifiers and low pass filters, and the voltage controlled oscillator consisted of crystals and amplifiers. Engineers have evolved the PLL into many different variants. The classic digital PLL (DPLL) is mostly analog, but replaces the phase detector with a digital implementation [1][4][7][16][18]. Next, the All Digital PLL (ADPLL) which replaced the loop filter with a digital equivalent and the voltage or current controlled oscillator with a numerically controlled oscillator[1][5]. There also exists a Software PLL which utilizes a microprocessor and Analog to Digital Converters (ADC) to over-sample the signals and use floating point or integer math to perform the phase detection and the loop filter portions of the loop[1]. Let's examine some of these architectures in more detail.

#### 1.2.1 Classic Digital PLL

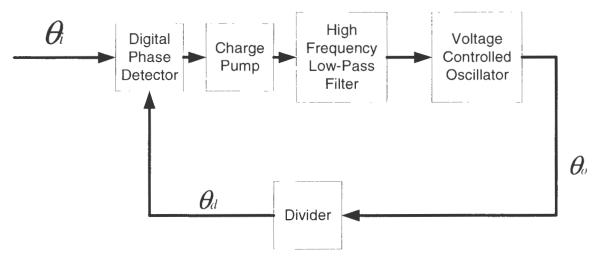

The classic digital PLL's used mostly analog components, however the phase-detector is replaced with digital gates, and often there exists a divider between the VCO and the phase detector. This enables the VCO to operate at higher rate than the reference and still maintain synchronization. There also exists a Charge Pump which is used to convert the digital outputs to an analog current or voltage[16]. This is a common architecture used today for both integrated and discrete PLL's[18]. The key benefits of this type of approach are its simplicity and more predictable linear behavior. However, this type of PLL is not flexible and adding programmability usually results in degraded performance because of extra loading on analog circuits.

Figure 3 : Digital PLL Diagram

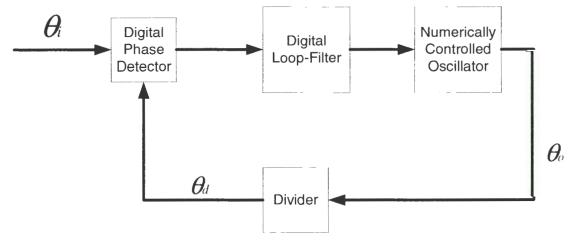

## 1.2.2 All-Digital PLL

The All-Digital PLL extends the digital circuits to include digital loop filter and numerically controlled oscillator. Often the digital loop filters include digital counters, multipliers, dividers, or other DSP type structures[7][14]. The numerically controlled oscillator takes as an input some number of binary bits of data and produces a square wave output at a specific frequency corresponding to the value of the input[5].

Figure 4 : All-Digital PLL Diagram

4

The primary benefits of this type of loop is that the majority of its components are digital. This provides simplicity in implementation and portability to may applications. Additionally digital circuits are easier to translate to different processes and scale well with Moore's Law. Programmability is also more easily added because digital circuits are not as susceptible to degradation because of loading. However, the ADPLL also behaves in a more non-linear manner. This results in the need for more difficult analysis techniques.

## 1.2.3 Software PLL

Software PLL's usually uses sampled data and standard mathematical functions for phase detector and loop filters[1]. This type of PLL uses a microprocessor with arithmetic computation units which operate at rates greater than the oscillator and reference. The benefits of such implementations are very low bandwidth operation, flexibility of loop parameters, and potentially very low noise. However a SPLL must operate at much slower rates because of the limits of the microprocessor.

## 1.3 Overview of Various PLL Components

### 1.3.1 Digital phase detectors

The phase detector is a critical component of any PLL and in modern PLL architecture the digital phase detector is by far the most prevalent. This section briefly discusses four common types of digital phase detectors.

### XOR Based Phase Detector:

The simplest digital phase detector consists of only an XOR gate[1].

Figure 5 : XOR Based Phase Detector

5

The output is a series of pulses with varying pulse widths. When locked the output has a 50% duty cycle. This type of phase detector integrates well with analog loop filters and is commonly used in the classic digital PLL's. The loop filter acts to create a RMS voltage from the series of pulses. In locked condition the reference and the oscillator are 90 degrees out of phase.

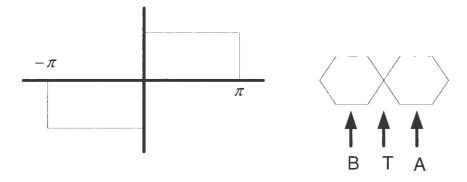

Figure 6 : XOR PD Response

It has a response as shown in Figure 6. The linear operating region is  $-\pi/2$  to  $\pi/2$ .

#### Phase Frequency Detector:

The Phase-Frequency Detector has 2 outputs which indicate Up and Down changes in frequency required. This detector expands the linear region to  $4\pi$  as shown in Figure 8. Also its outputs are dependent only on the rising edges of the inputs. This eliminates dependencies on the duty cycle of the inputs. This phase detector is widely used in fully integrated classic digital PLL's because its outputs allow more direct connection to charge pump circuits[1][16-18] and its large linear region.

Figure 7 : Phase-Frequency Detector

Figure 8 : PFD Response

Alexander (Bang-Bang) Phase Detector:

This phase detector is widely used in clock data recovery applications because it produces a sample of the data as well as phase error information. Additionally, it recognizes when there has been no transitions[1][2-4][13-14]. This is important so that no adjustments to the loop are made without transitions. Additionally, the outputs are synchronous digital signals and integrate well with all digital PLL's. The phase error information is not dependent on amplitude, duty cycle, or frequency of the phase detector outputs as they are with the other digital phase detectors discussed.

Figure 9 : Alexander (Bang-Bang) Phase Detector

Figure 10 : Bang-Bang PD Response

#### 1.3.2 Charge Pumps and Loop Filters

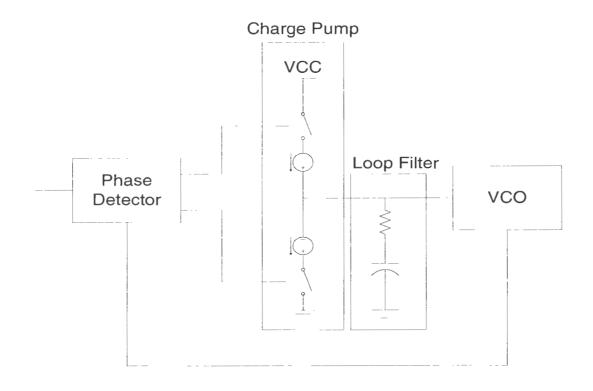

A Charge Pump is used in many classic digital PLL's, especially the fully integrated. Its purpose is to convert the digital signals to analog current or voltage level suitable for a current or voltage controlled oscillator. Gardner[16] was one of the first to produce a paper describing charge pump operation. The charge pump operates by turning on or off one or more current sources. Figure 11 illustrates a common integrated charge pump architecture. Analog loop filters can be grouped as either active or passive. A passive loop filter would consist of a single pole low pass filter constructed from a resistor and a capacitor similar to Figure 11; while an active loop filter would contain an amplifiers and gain control. Loops

greater than 2<sup>nd</sup> order are rarely used because of stability issues[1]. A Digital loop filters would consist of accumulators, integrators and gain control[1][7][14].

Figure 11 : Example Charge Pump and Loop Filter

#### 1.3.3 Controlled Oscillators

There are many types of controlled oscillators depending on whether they are integrated inside of an IC or external. The basic integrated versions are the ring oscillator and the LC oscillator[8][9]. A ring oscillator consists of a series of buffers or inverters forming a feedback loop. The delay of each buffer is controlled via the control voltage or current. In most cases the delay is adjusted using a voltage control capacitor or varactor. An initial signal is injected into the ring and as long as the total gain of the ring is greater than or equal to 1 it will continue to oscillate. If the individual stages or buffers of the ring oscillator are well matched, it is easy to generate multiple phases of the output clock which is an advantage in many architectures. The LC or tank oscillator consists of an inductor and capacitor connected in parallel. The tuning range of LC oscillators is usually much narrower than ring

oscillators due to the difficulty in changing the inductance value. However, LC oscillators have much lower phase noise than ring oscillators[8]. External controlled oscillators are usually based on quartz crystal technologies using either Bulk Acoustic Wave(BAW) or Surface Acoustic Wave(SAW) technologies[11][12]. There is also now published work demonstrating the use of crystal based technology in on chip or integrated applications[10]. Crystal based oscillators are among the lowest noise solutions available.

## 1.4 Thesis contribution

In this final section of the introduction the architecture and design which was developed for this thesis will be introduced. The design utilizes a FPGA, DAC and VCXO. The major contributions of this thesis are:

- 1. An all digital PLL were designed, implemented, and characterized.

- 2. The design is flexible and can be adapted to many applications.

- 3. The design is scalable to many process technologies.

- 4. The design can be adapted to lower or higher frequencies.

- 5. The design produces a very low noise clock.

- 6. The design implemented is relatively low cost using inexpensive components.

- 7. The design can be used to filter noise in other clock or data signals.

- 8. The design allows the bandwidth of the loop to be adjusted dynamically allowing for faster acquisition time and increased filtering capability.

- 9. The design can be used in clock and data recovery applications.

- 10. The design introduces a modified phase detector and loop filter architecture which produces a more linear response than traditional bang-bang phase detectors.

- 11. An automated jitter transfer test was developed to analyze the loop performance.

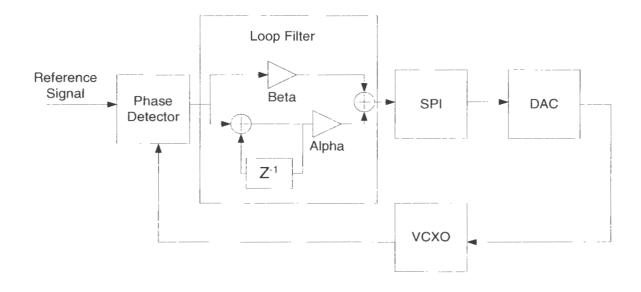

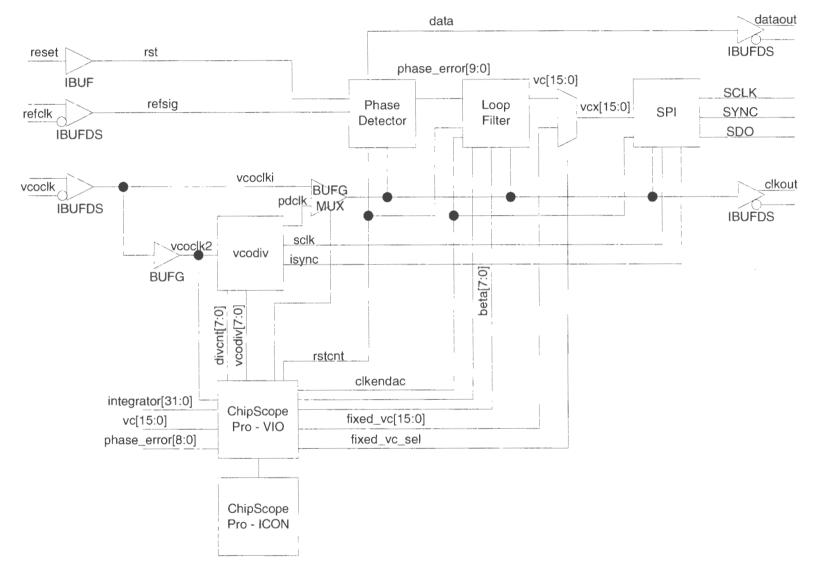

Figure 12 on the following page illustrates the basic architecture used.

#### 1.4.1 Architecture and Design

An Alexander or Bang-Bang phase detector was selected for implementation for primarily two important reasons. This phase detector works very well as a clock and data recovery phase detector since it is able to ignore periods where there are no transitions[1]. Secondly, it is a synchronous digital output which can be integrated easily with digital loop filter circuits. This allows greater flexibility in applications and reduces the need for specific divider ratios on the reference clock. Additionally, if the reference signal is intermittent, the loop will maintain its present frequency which is a benefit in many applications. One unique feature of the implemented phase detector is that it operates at a much higher sample rate than the loop filter and DAC. Figure 13 shows a Sample Clock going to the Loop Filter. This clock is an integer divide from the VCO Clock which enters the FPGA. The result is that the phase detector output becomes a 9 bit signed integer. This makes the phase detector operate more linear because the output of the phase detector is not a +1 or -1 as is the common implementation of bang-bang phase detectors. The output gain of any bang-bang phase detector will be dependent on the jitter or phase noise present on the reference signal and the clock inputs[2][3][14].

Figure 12 : Simplified Design Architecture

The design implements a digital loop filter which has both first order and second order paths. The first order path contains the gain control Beta and controls the response to small changes in phase, while the second order path contains the gain control Alpha and helps to maintain stability and responds to larger frequency and phase steps and maintains the DC offset required by the VCXO. The SPI interface is a serial to parallel circuit which receives the 16bit data from the loop filter and creates a serial stream of bits for the DAC. A survey

of available DAC devices was performed. There are two basic classes of DAC's available off the self. The first is the inexpensive, low frequency type which operate at update rates less than 1Msample/second. These DAC's are available with resolutions between 10 to 16 bits. The cost of these DAC's is between \$1 and \$8. The second class is the more expensive high frequency type which operate at rates greater than 1Msample/second. These DAC's have parallel interfaces and use large packages. The resolutions available is between 12 and 24 bits and are tailored for wireless applications. The cost of these DAC's is usually greater than \$20. The design implemented uses the inexpensive, lower frequency DAC which are available from a variety of vendors. It will be shown that there is only a very small penalty in added quantization noise resulting from the use of the slower more inexpensive DAC.

## 1.5 Analysis of implemented loop parameters

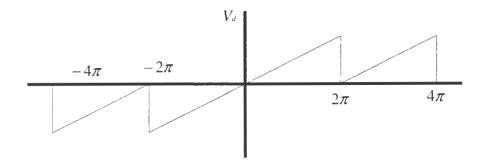

#### 1.5.1 DAC Resolution and Sample Rate

To determine the effect of DAC resolution and update rate on the overall jitter of the system Equation (2) should be considered.

$$J_{Q}(s) = \left(\frac{1}{1 - \frac{R * K_{dac} * K_{v}}{10^{6}}}\right) - \left(\frac{1}{1 + \frac{R * K_{dac} * K_{v}}{10^{6}}}\right) * \frac{1}{F_{s}}$$

(2)

Where R is the assumed orbit radius[3],  $K_v$  is the VCXO gain in parts per million (ppm), and  $F_s$  is the update rate of the loop filter and DAC. The DAC gain is defined by Equation (3).

$$K_{dac} = \frac{V \max - V \min}{2^{N}} \tag{3}$$

For this implementation we are using a 12bit DAC resulting in  $K_{dac}$  equal to 0.8mV/bit. Fs is equal to 1.15Mhz,  $K_v$  is 390ppm, and an estimated R = 3. Therefore we could expect  $J_Q$  approximately equal to 1.6ps p-p.

#### 1.5.2 Loop Filter Gain

Due to the non-linear characteristics of this type of ADPLL, the analysis has not been widely published. Nicola Da Dalt published a time domain analysis[3] of a very similar PLL. His paper determined that there existed a minimum value of Beta for a given D and Alpha. D is the delay of the system.

$$\beta_{\min} = \frac{\alpha^* (1+2^*D)}{2} \tag{4}$$

Additionally Da Dalt determined that there existed an optimal value of Beta such that minimum jitter would be possible due to minimization of the orbits[3].

$$\beta_{opt} = (1.3846 + 1.8846 * D) * \alpha$$

<sup>(5)</sup>

It must be noted that the references to Beta in the design and measurement sections is somewhat different than Da Dalt's and the introduction chapter of the thesis. Da Dalt refers to Beta and Alpha as pure gain. In the design of this ADPLL Alpha and Beta are related to gain via Equations (6).

$$\beta_{gain} = 2^{-Beta} : \alpha_{gain} = 2^{-Alpha}$$

### **1.6** Conclusion

In this chapter the basic set of PLL architectures where discussed. The components of these PLL's where also described and compared. Finally, the specific design implemented in this thesis was also introduced as well as supporting analysis of jitter performance and stability.

## **Chapter 2 Implementation**

#### 2.1 Introduction

This chapter describes the detailed implementation of the all digital PLL. Each module or block of the design will be described including input and output signal names and functionality. Additionally the supporting circuits used for control and status monitoring and user interface which was used during characterization will also be described.

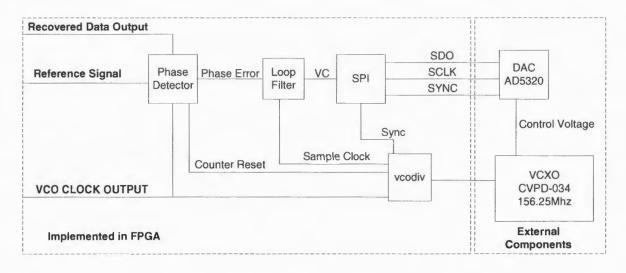

#### 2.2 Design

The design was implemented with digital circuits designed using Verilog HDL. The design was compiled, synthesized, and fitted into a Virtex-II ProX FPGA. The FPGA was connected to external components as shown in Figure 13. The external components consist of a low cost 12 bit digital to analog converter (DAC) Analog Devices AD5320 and a voltage controlled crystal oscillator (VCXO) Crystek CVPD-034 operating with center frequency of 156.25Mhz. The ADPLL design consumes less than 178 slices, which is 1% of the V2PX20 FPGA used and ~13% of the smallest Virtex-II Pro device that Xilinx makes, the 2VP2. A slice is a standard logic block which all Xilinx FPGA's are built. This design can easily fit into a device that is also supporting other functions without requiring extra expense or larger device. This design could also be implemented in low cost CPLD technology such as the Xilinx CoolRunner II product family if an FPGA was not already present on the circuit card. Figure 23 provides a detailed diagram of the circuits inside the FPGA including supporting circuits to allow testing. Appendix A contains the Verilog HDL source code for the FPGA circuits. The top level verilog HDL source file is available in Appendix A and is named "fpga\_top.v".

Figure 13 : Simplified System Level Diagram

Figure 14 : Accumulating Bang-Bang Phase Detector

#### 2.2.1 Phase Detector

An Alexander phase detector as depicted in Figure 9 was augmented with a decoder and up and down counters. This was done to create the accumulating bang-bang phase detector depicted in Figure 14. The accumulating bang-bang phase detector allowed the phase detector to operate at a higher rate than the loop-filter and DAC. This is important when a low speed DAC converter is used. The Phase Error is represented by a 9 bit signed integer instead of the typical single signed bit of an Alexander phase detector. The decode operation for the phase detector is illustrated in Table 1. Both Invalid and No transition cases do not cause the up and down counters to increment. In a low transition case this allows the VCXO to maintain a constant frequency. This approach does not have the same limitations as an analog or classic digital PLL. A PLL with an analog loop filter and a charge pump would tend to drift downward in frequency in the absence of transitions due to leakage currents and loss. The up and down counters are reset whenever the phase error signal is sampled by the loop filter. The Verilog HDL source file is in Appendix A and is named "pd.v".

| A | Т | В | Description    |

|---|---|---|----------------|

| 0 | 0 | 0 | No transitions |

| 0 | 0 | 1 | Down           |

| 0 | 1 | 0 | Invalid        |

| 0 | 1 | 1 | UP             |

| 1 | 0 | 0 | UP             |

| 1 | 0 | 1 | Invalid        |

| 1 | 1 | 0 | Down           |

| 1 | 1 | 1 | No transitions |

Table 1 : BBPD decode table

Figure 15 : Accumulating Phase Detector Input Output Diagram

| Signal Name      | Description                                       |  |

|------------------|---------------------------------------------------|--|

| refsig           | Reference signal may be a clock or data signal    |  |

| rstent           | Counter Reset signal                              |  |

| reset            | Resets the phase detector flip-flops              |  |

| vcoclk           | clock signal from the VCO or VCXO                 |  |

| data             | sampled data output synchronous to vcoclk         |  |

| phase_error[8:0] | 9 bit signed integer representing the phase error |  |

Table 2 : Accumulating Phase Detector Input Output Description

#### 2.2.2 Loop Filter

Figure 16 : Digital Loop Filter Implementation

The loop filter consists of a first order path which is just a gain stage and a second order path which is an integrator/accumulator followed by a gain stage. The first order gain is controlled via input beta and divides the input value by 2<sup>beta</sup>. The second order gain is controlled by input alpha and divides the accumulated value by 2<sup>alpha</sup>. Because it divides only by multiples of 2, the dividers can be simplified to binary right shifts. This is important for implementations using standard digital gates because it reduces the complexity and size of the dividers. However, in applications where multipliers are available such as the DSP blocks in the Xilinx Virtex 4 FPGA, it would be better to use true multiplies in order to give better control of loop parameters.

Figure 17 : Loop Filter Input Output Diagram

| Signal Name      | Description                                                               |

|------------------|---------------------------------------------------------------------------|

| vcoclk           | clock signal from VCO or VCXO                                             |

| clkendac         | clock enable signal used for all registers                                |

| phase_error[8:0] | 9 bit signed integer representing phase error                             |

| alpha[7:0]       | controls 2 <sup>nd</sup> order loop gain                                  |

| beta[7:0]        | controls 1 <sup>st</sup> order loop gain                                  |

| rstent           | identifies when to sample the phase_error signal                          |

| rstint           | Reset the integrator registers                                            |

| vc[15:0]         | 16 bit unsigned integer output representing the Control Voltage           |

| integrator[31:0] | 32 bit unsigned output of the integrator value used for monitor and debug |

Table 3 : Loop filter Input Output Description

In this implementation the Sample Clock is the VCO output clock, however it is controlled by the signal clkendac which acts as a clock enable. This results in an effective clock which is divided from the VCO clock. The rate of this Sample Clock is controlled by the vcodiv circuit and the input control signal divent. The signal divent should be set so that the period of the Sample Clock is greater than the minimum period allowed by the DAC; in this case 50ns. The Verilog HDL source file for the loop filter is in Appendix A and is named "lp.v".

#### 2.2.3 SPI – Serial Peripheral Interface

The Serial Peripheral Interface is a standard interface which provides the communication of the 12 bit DAC value through a 3 wire serial interface. Most microcontrollers and processors support similar interfaces. Using this interface allows flexibility in the DAC design; the same pin out and package can be used for many different DAC models allowing pin for pin compatibility for 8bit to 16 bit DAC's. Additionally using a serial interface reduces the size of the external DAC package. This is important so that the design can maintain only a small amount of space on the printed circuit board. The Verilog HDL source file for the serial peripheral interface is in Appendix A and is named "spi.v".

Figure 18 : SPI Input and Output Diagram

| Table 4 : | SPI | Input | and | Output | Description |

|-----------|-----|-------|-----|--------|-------------|

|-----------|-----|-------|-----|--------|-------------|

| Signal Name | Description                                |

|-------------|--------------------------------------------|

| clk         | clk input used for all registers           |

| clkendac    | clock enable signal used for all registers |

| data[15:0]  | data to be sent to DAC                     |

| sclki       | input clock for DAC interface              |

| isync       | input sync signal for DAC interface        |

| bitsel[3:0] | identifies which bit of data goes to DAC   |

| SCLK        | Buffered sclki driven to DAC               |

| SYNC        | buffered isync driven to DAC               |

| SDO         | Buffered data[bitsel] driven to DAC        |

## 2.2.4 VCO Divider (vcodiv)

This block is responsible for creating the clocks, clock enables and sync pulses used by the other circuits in the design.

Figure 19 : VCODIV Input/Output Diagram

The outputs of this block synchronize the sampling of the accumulating phase detector, reset of the counters, calculations in the loop filter and the transmission of the DAC value thru the SPI to the DAC.

| Pin Name    | Description                                                                 |

|-------------|-----------------------------------------------------------------------------|

| clk         | This is the input clock from the VCXO                                       |

| divent[7:0] | Divider value for the Sample Clock                                          |

| vcodiv[3:0] | Divider value for the pdclk                                                 |

| pdclk       | clk divided by vcodiv                                                       |

| sclk        | clk divided by divent driven out of the FPGA to DAC                         |

| sync        | pulse occurs 1 every 17 cycles is used by SPI block                         |

| bitsel[3:0] | identifies the bit which should be send out the SPI block                   |

| clkendac    | clock enable signal for loop filter, spi blocks pulse identifies the rising |

| -           | edge of sclk                                                                |

| rstcnt      | Counter Reset signal used to reset the up and down counters in the phase    |

|             | detector                                                                    |

Table 5 : VCODIV Input and Output Description

The inputs divent and veodiv control the rate of the output clock and clock enable signals, clkendae. The pdclk signal is the clk signal divided by veodiv. This output clock can be selected to drive the phase detector VCOCLK signal if the VCXO is too fast for the FPGA fabric. This would be the case if the VCXO where operating at greater than 200Mhz. However this operation was not used or required during the characterization of this design. The clkendae signal is a pulse with duration equal to the period of the signal clk. It is used as a clock enable signal by the loop filter and SPI interface so that only a single global clock signal veoclk is used by FPGA logic. The signal divent is used to determine the rate of the clock enable. The signal selk is a 50% duty cycle version of this which is driven out of the FPGA to the DAC. The Verilog HDL source file is provided in Appendix A of this thesis and is named "veodiv.v".

#### 2.2.5 Digital to Analog Converter

The DAC used for this implementation is an Analog Devices AD5320 device[15]. This device has several important advantages. First, it is a low-cost DAC with a volume price less than \$2. Second, it is very small package which saves space on the PCB board.

Figure 20 : AD5320 Diagram

#### 6-Lead Small Outline Transistor Package [SOT-23] (RT-6)

Dimensions shown in millimeters

COMPLIANT TO JEDEC STANDARDS MO-178AB

Figure 21 : AD5320 Package Diagram

### 2.2.6 Voltage Controlled Crystal Oscillator

The VCXO used for this implementation was produced by Crystek, Inc. The specifications as stated in the product data sheet are illustrated in Table 6[14]. The  $K_v$  or gain associated with the this VCXO was not provided in the datasheet. However, it was measured to be approximately 390ppm.

## Table 6 : VCXO specifications

| Frequency Range:   |                           | 77.760MHz to 200MHz                       |

|--------------------|---------------------------|-------------------------------------------|

| Temperature Range: |                           | 0°C to 70°C                               |

| (Option M)         |                           | -20°C to 70°C                             |

| (Option X)         |                           | $-40^{\circ}$ C to $85^{\circ}$ C         |

| Storage:           |                           | -55°C to 120°C                            |

| Input Voltage:     |                           | $3.3V \pm 0.3V$                           |

| Control Voltage:   |                           | $1.65V \pm 1.65V$                         |

| Settability At     |                           |                                           |

| Nominal:           |                           | $1.65V \pm 0.25V$                         |

| Input Current:     |                           | 50mA Typ, 88mA Max                        |

| Output:            |                           | Differential LVPECL                       |

|                    | Symmetry:                 | 45/55% Max @ 50% Vdd                      |

|                    | Rise/Fall Time:           | lns Max @ 20% to 80% Vdd                  |

|                    | Pulling Range:            | ±50ppm APR Min. (std)                     |

|                    | Linearity:                | ± 10% Max                                 |

|                    | Logic: Terminated to      |                                           |

|                    | Vdd-2Vinto                | 50 ohms                                   |

|                    | Temp. 0°C to 85°C         | "0" = 1.490 Min, 1.680 Max                |

|                    |                           | "1" = 2.275 Min, 2.420 Max                |

|                    | Temp40°C to $0^{\circ}$ C | "0" = 1.470 Min, 1.745 Max                |

|                    | Enable/Disable Time       | "1" = 2.215 Min, 2.420 Max                |

|                    |                           | 200ns Max                                 |

| Jitter:            | 12KHz to 80MHz            | 0.5psec Typ., 1psec RMS Max               |

| Phase Noise:       | 10Hz                      | -60dBc/Hz Typical                         |

| (Ref: 122.88MHz)   | 100Hz                     | -95dBc/Hz Typical                         |

|                    | 1KHz                      | -120dBc/Hz Typical                        |

|                    | 10KHz                     | -140dBc/Hz Typical                        |

|                    | 100KHz                    | -145dBc/Hz Typical                        |

| Aging:             |                           | <5ppm 1st/yr, <2ppm every year thereafter |

## 2.2.7 ChipScope Pro

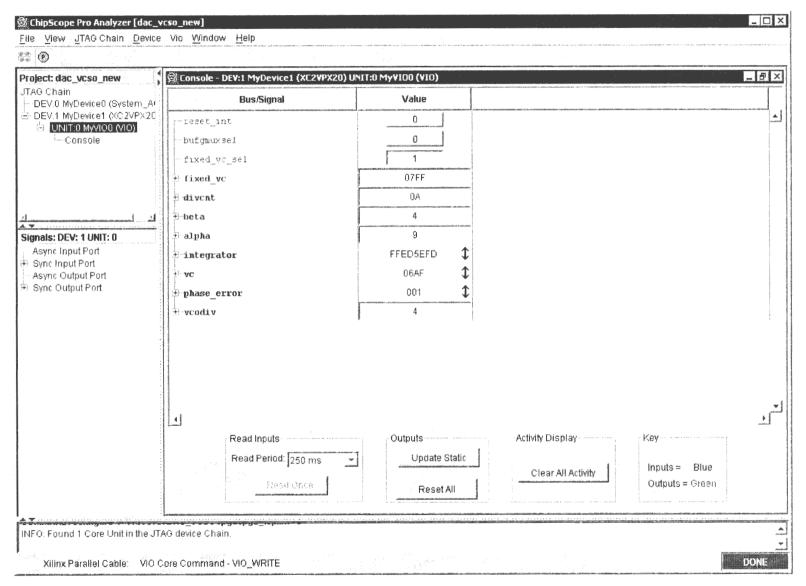

ChipScope Pro is a tool offered by Xilinx as a way to control and monitor internal circuits inside the FPGA. Two ChipScope Pro blocks were added to the design in order to facilitate the control and monitoring of the parameters listed in Table 7. Figure 22 provides a screen capture of the ChipScope Pro control panel as it was used with this design.

| Signal Name      | Description                                                             |

|------------------|-------------------------------------------------------------------------|

| divcnt[7:0]      | Controls the divider which creates the Sample clock it should be set so |

|                  | that the period of the sample clock is greater than the minimum period  |

|                  | of the DAC                                                              |

| vcodiv[3:0]      | Controls the divider of the clock going to the phase detector. Not      |

|                  | usually used unless VCO is too fast for the FPGA logic                  |

| BUFGMUXSEL       | Selects the divided vco clock or the vco clock directly                 |

| alpha[7:0]       | controls the 2 <sup>nd</sup> order loop gain                            |

| beta[7:0]        | controls the 1 <sup>st</sup> order loop gain                            |

| rstint           | resets the integrator registers                                         |

| integrator[31:0] | monitors the integrator value                                           |

| phase_error[8:0] | monitors the phase_error value                                          |

Table 7 : Programmable settings and monitors

The Chipscope Pro blocks contribute significantly to the total area of the design used for characterization. However, in a real system design these blocks would not be necessary because either the design would be fixed to certain parameters or the would exist some other method to control loop parameters. The logic blocks which were added to the design are ICON and VIO blocks. The ICON block is the control portion of ChipScope and VIO is a synchronous input and output block. The control and status signals are connected to the VIO block to allow access via this graphical user interface. The ChipScope blocks do not have source files associated with them. They get merged during the FPGA compile process. Figure 23 shows how these blocks are connected to the rest of the ADPLL design.

Figure 22 : ChipScope Pro Screen Capture

25

Figure 23 : Detailed Diagram of FPGA

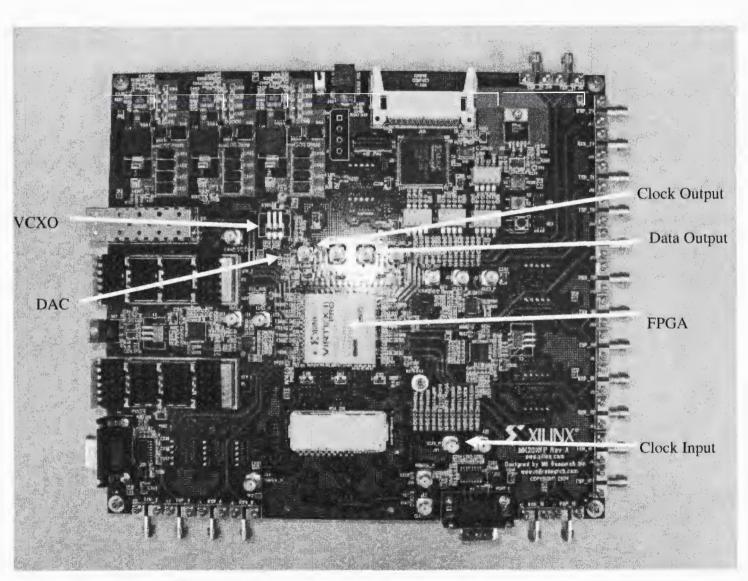

## 2.3 FPGA compile and P&R

The entire design including Chipscope Pro cores was processed through the Xilinx ISE version 6.3.03i tools set. This included using the Xilinx Synthesis Tool (XST) to synthesize the verilog HDL files to EDIF format. Xilinx translate tool was used to combine the EDIF files from the synthesized design and the Chipscope Pro cores and the Coregen adder circuits into a complete design file. This design file is then processed by the Xilinx map tool which maps gates to FPGA slices. This design is then processed by the Xilinx par tool which generates a completely placed and routed design. The final step is to convert this design to a bit-stream file which can be programmed into the FPGA via the JTAG programming port. The design consumed 1226 Slices or 12% of the target device XC2VPX20. The majority of this was consumed by the Chipscope Pro cores which contain a lot of internal memory cells. When the DPLL is compiled without the ChipScope Pro blocks and all of the control signals such as alpha[7:0], beta[7:0], divent[7:0], etc are brought to input pins the ADPLL alone consumes only 178 Slices or 1% of the 2VPX20 FPGA. The design will operate at up to 172Mhz according to the static timing analysis performed by the Xilinx tools. All data was taken using a 156.25Mhz VCXO and 78.125Mhz Reference Signal. The printed circuit board used to test the design is a MK20XFP board which was co-developed by Xilinx, Inc and M6 Research, Inc. contains a picture of the board used.

### 2.4 Conclusion

In this chapter of the thesis the ADPLL design was described in detail. Each block associated with the design was describe and the input and output signals identified. Additionally, the ChipScope Pro interface was shown and the control and status signals where described. Finally, all verilog HDL source files for each module is provided in Appendix A of this thesis.

Figure 24 : Picture of MK20XFP Board

# **Chapter 3 Measured Results**

### 3.1 Introduction

This chapter of the thesis is intended to present all data taken on the implementation as it was tested on the MK20XFP board as shown in Figure 24 utilizing the Xilinx Virtex-II ProX FPGA, Analog Devices AD5320 DAC, and Crystek 156.25Mhz VCXO. The individual parameters of the design were varied in order to analyze their impact on performance, bandwidth, and stability. Additionally, the test setups and automation software which was developed in order to acquire the data will also be described.

#### 3.2 Measurement Setup

There were two basic test setups used to analyze the performance of the implemented ADPLL circuit. The first was a reference source and a spectrum analyzer which was used for jitter transfer, jitter generation, and frequency step response. The second was a Bit Error Rate Tester (BERT) using reference clock sources which was used only for jitter tolerance testing. This setup is a 12Gbps BERT test system developed by Hewlett-Packard before the company split off into Agilent. It has the ability to operate from 10Mhz to 12Gbps. Test Setup #1 was used for the majority of the testing including Jitter Transfer, Jitter Generation and Frequency Step Response. Test Setup #2 was used only for the Jitter Tolerance Test.

| Manufacturer | Model<br>Number | Description                                                 |

|--------------|-----------------|-------------------------------------------------------------|

| Agilent      | 33250           | Function / Arbitrary Waveform Generator, 80 MHz             |

| Agilent      | E4407B          | E4407B ESA-E Series Spectrum Analyzer<br>100 Hz to 26.5 GHz |

| Agilent      | infinuim        | 4Gs/s, 2.5Ghz Digital Storage Oscilloscope                  |

| Table 8 | • | Equipment  | List | for | Test  | Setun | #1 |

|---------|---|------------|------|-----|-------|-------|----|

| raute o | • | Lyuipinein | LISU | 101 | I Cot | Sciup | 01 |

| Manufacturer | Model<br>Number | Description                |

|--------------|-----------------|----------------------------|

| Agilent      | 83752A          | Signal generator           |

| HP           | 70004A          | Display                    |

| HP           | 70843B          | Error Performance Analyzer |

| HP           | 3325B           | Signal generator           |

Table 9 : Equipment List for Test Setup #2

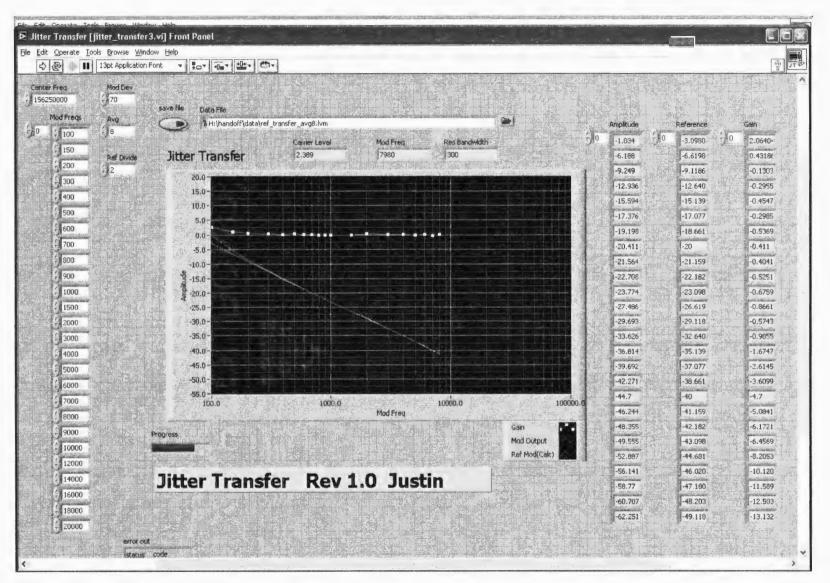

#### 3.3 Labview Automation

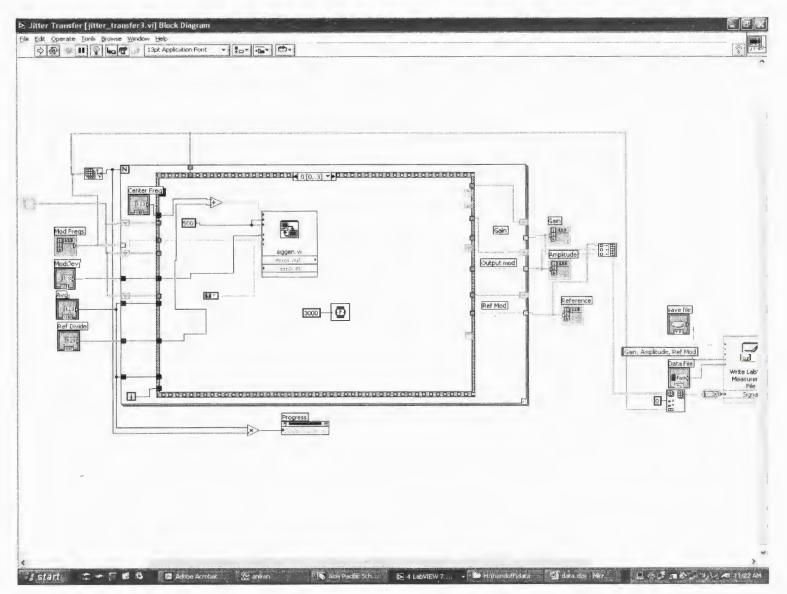

In order to facilitate repeatable and numerous measurements, National Instruments Labview software was used to develop an automated Jitter Transfer Measurement using a test setup #1 as described in Table 8. Using the Labview software two virtual instruments (VI's) were developed. The first, Jitter\_Transfer3.vi, configures the reference source to generate a reference clock at defined frequency with a defined amount of modulation. Then using the spectrum analyzer it measures the modulation amplitude present on the signal under test. This is repeated for a number of different Modulation frequencies. Labview VI's are constructed graphically first by constructing a Front Panel which consist of controls and indicators. The Front Panel represents the Graphical User Interface of the instrument. Figure 25 shows the Front Panel for the Jitter\_Transfer3.vi Block. The operation of the program behind the Front Panel is represented by the Block Diagram. The Block Diagram is formed by connecting different controls and indicators from the Front Panel represented by icons to functions and sub-vi's using wires. Figure 26 shows the Block Diagram for the Jitter\_Transfer3.vi. As can be seen from the Front Panel this VI receives a list of modulation frequencies, modulation frequency, center frequency, averages, and reference divide ratio. It outputs 3 vectors which are also plotted on the graph on the front panel. The vectors are modulation gain, input modulation amplitude which is calculated using Equation (7), and measured output modulation amplitude. As can be seen there is very good correlation between the two graphs. This data is recreated in Figure 30.

Figure 25 : Jitter Transfer3.vi Front Panel

Figure 26 : Jitter Transfer3.vi Block diagram

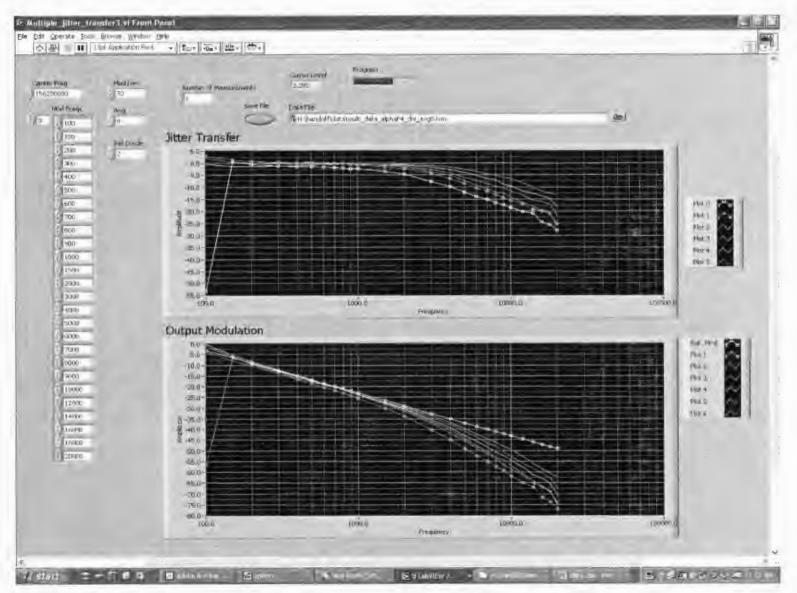

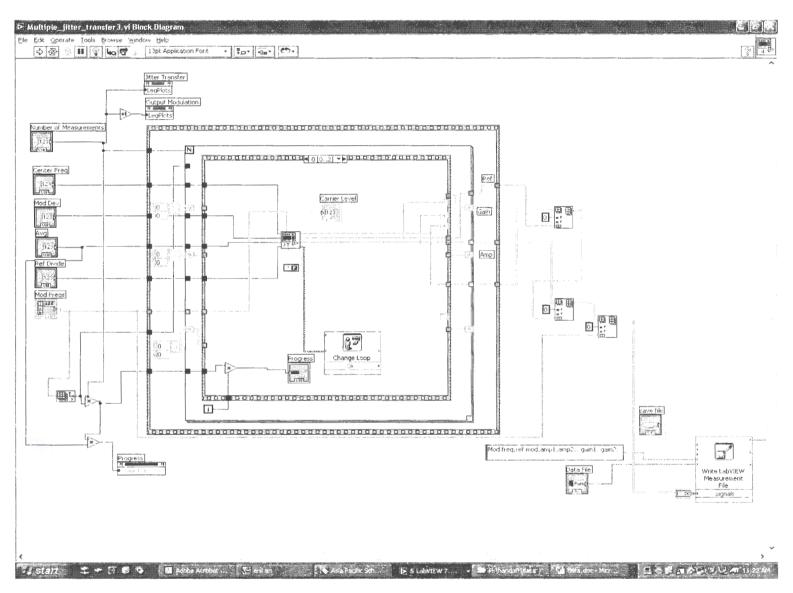

The second VI, Multiple\_jitter\_transfer3.vi, calls the first VI, Jitter\_Transfer3.vi, multiple times pausing between each call to allow for changing loop parameters via ChipScope Pro control panel. During each iteration of Jitter\_Transfer3.vi, the data is graphed on separate amplitude and gain graphs for immediate feedback on progress and performance. Figure 27 shows the Front Panel of Multiple\_jitter\_transfer3.vi which receives the same basic inputs as Jitter\_Transfer3.vi and passes them directly to Jitter\_Transfer3.vi. The output is a series of graphs. The top graph shows data collected from each iteration through Jitter\_Transfer3.vi and the comparison of the effects of the different parameter changes. This data is also saved to a data file which was later imported into a spreadsheet which recreated the graphs for inclusion in this thesis. The top graph shows the jitter transfer or modulation gain, the second graph shows just the modulation amplitude that was measured. Figure 28 shows the Block Diagram for the Multiple\_jitter\_transfer3.vi. Central in the VI diagram is the icon for the Jitter\_Transfer3.vi sub-vi. It is shown along with the function block which pops-up a dialog box to request the loop parameter change. The Labview software uses the General Purpose Instrument Bus (GPIB) to communicate with both pieces of equipment.

Figure 27 : Multiple\_jitter\_transfer3.vi Front Panel

34

Figure 28 : Multiple\_jitter\_transfer3.vi Block Diagram

## 3.4 Jitter Transfer

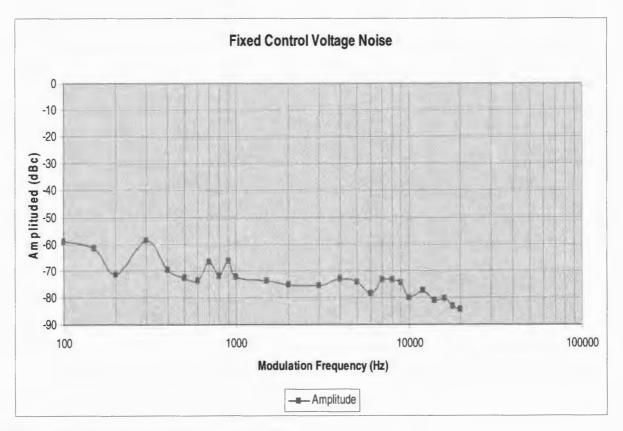

Using the Labview VI's some calibration measurements were taken in order to get an idea of the amount of noise present in the VCXO and the FPGA output drivers. A baseline noise measurement was taken with the DAC set to a fixed value of 0x6F0. This is shown in Figure 29. This graph establishes the noise floor of the DAC and FPGA at about -60dBc to -70 dBc.

Figure 29 : Fixed Control Voltage Noise Plot

Figure 30 : Reference Modulation Plot

Next a measurement was taken to correlate the calculated value of Reference modulation amplitude relative to the actual measured value using the equipment. Amplitude of the reference modulation, A(dBc) is calculated by the following equation.

$$A(dBc) = 20 * \log\left(\frac{Fdev * Nref}{F \mod 2}\right)$$

<sup>(7)</sup>

Where Fdev is the frequency of the deviation, Fmod is the modulation frequency and Nref is the reference divide ratio. The reference divide ratio is usually 2, because the VCXO frequency is twice the reference frequency. Notice the two values correlate very well with only minor differences due to noise.

37

Figure 31 : Jitter Transfer Amplitude Alpha=0xC

Figure 32 : Jitter Transfer Gain Alpha=0xC

In order to analyze the effects of the parameter Beta a fixed value for Alpha was chosen such that all possible values of Beta would result in stable operation of the ADPLL. Figure 31 and Figure 32 illustrate these measurements. Gain is calculated by subtracting the calculated reference modulation amplitude from the measured output amplitude for each modulation frequency. The data points taken at 200Hz and less should be considered to be marginal measurements since these measurements are taken near the limits of the spectrum analyzers specified operating range. Some false or invalid measurements were observed in this range during the course of testing. Additionally, measurements of amplitude less than -65dB are not as accurate since this is the approximate noise floor of the test system. With this in mind we can see that as Beta increases the closed loop bandwidth of the system decreases. Where as a Beta = 0 results in a bandwidth of approximately 10Khz; a Beta = 4 results in a bandwidth of 1.5Khz. It is also noticed that as the value of beta approaches the value of alpha the modulation gain starts to show peaking or positive gain.

Figure 33 : Jitter Transfer Amplitude Alpha=0xF

Figure 34 : Jitter Transfer Gain Alpha=0xF

These measurements where repeated with an Alpha=0xF which is its maximum value. It is shown that increasing Alpha also reduces closed-loop bandwidth of the system. This is shown by comparing Figure 34 and Figure 32. In fact it can be seen that with Alpha = 0xF and Beta > 4 the closed loop bandwidth of the system is less than what can be measured by the equipment used or less than 100hz.

In order to investigate this issue further data was taken with a fixed value of Beta=5 and Alpha was varied from 0x9 to 0xF. This data is shown in Figure 35 and Figure 36.

Figure 35 : Jitter Transfer Amplitude Beta=5

Figure 36 : Jitter Transfer Gain Beta=5

It is important to point out the increased peaking of the jitter transfer function as Alpha approaches Beta. In fact peaking is evident whenever Alpha < Beta + 8. It was also observed that the ADPLL appeared stable anytime Alpha < Beta + 3.

Next a value of Alpha and Beta were chosen for good stability and peaking performance and the divent parameter was changed from a value of 8 to a value of 0x18. This value did affect the closed loop bandwidth slightly; however the impact was significantly less pronounced than the effect of Alpha and Beta on closed-loop bandwidth. This can be seen in Figure 38. This affect is most likely due to the increased phase detector gain resulting from reduced update rate of the loop filter.

Figure 37 : Jitter Transfer Amplitude Alpha=0xF;Beta=4

Figure 38 : Jitter Transfer Gain Alpha=0xF;Beta=4

## **3.5 Jitter Generation**

Jitter generation was evaluated using the phase noise measurement capability of the spectrum analyzer in test setup #1. The bandwidth of consideration is from 10Khz to 10Mhz. The lower limit of 10Khz is the limit of the equipment. First the Reference Source was measured with no modulation present. The value of 0.4299 Degrees shown in Figure 39 is the total noise present in the band of interest. This equals 7.64ps RMS jitter from Equation (8).

| 🔆 Agilent                  | 23:15:46 Feb 19, 2005 T              | Measure              |

|----------------------------|--------------------------------------|----------------------|

| Ref -50dBc<br>#Samp<br>Log | /Hz #Atten 5 dB                      | Setup                |

| 10                         |                                      | Measure<br>Log Plot  |

| Start 10.6                 | 0 kHz Frequency Offset Stop 10.0 MHz | Measure<br>Spot Freq |

| Carrier Fre                | aq 78.1250 MHz                       |                      |

| Log Plot                   |                                      |                      |

| Noise                      | -100.81 dBc/Hz Spot Freq 10.0000 kHz |                      |

| RMS                        | 0.0075 Rad Lower Limit 10.0000 kHz   |                      |

|                            | 0.4299 Deg Upper Limit 10.0000 MHz   |                      |

| STORNES. S                 | IF file saved                        |                      |

Figure 39 : Phase Noise Measurement Reference

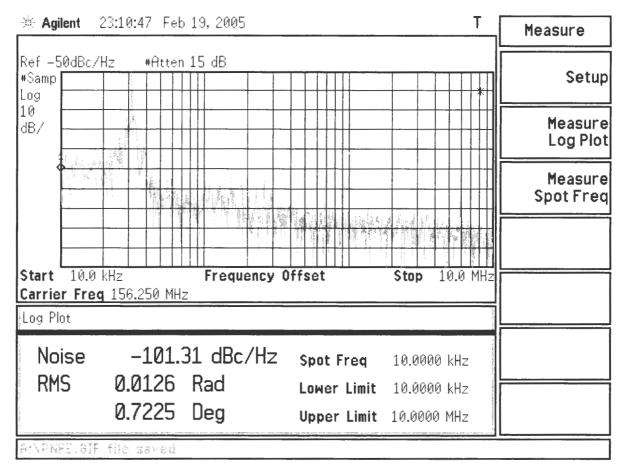

The system was measured first with a fixed DAC value so that the VCXO and the drivers of the FPGA could be measured. Using Equation (8), a value of 2.22ps RMS jitter was calculated for the fixed DAC value. It is important to point out that when measured directly at the output of the VCXO this value is approximately 1ps RMS. The difference can be attributed to the noise present in the FPGA

| 🔆 Agilent                   | 23:14:11 Feb 19, 2005 T                                                                                          | Measure              |

|-----------------------------|------------------------------------------------------------------------------------------------------------------|----------------------|

| Ref -50dBc,<br>#Samp<br>Log | /Hz #Atten 15 dB                                                                                                 | Setup                |

| 10<br>dB/                   |                                                                                                                  | Measure<br>Log Plot  |

|                             |                                                                                                                  | Measure<br>Spot Freq |

|                             | ) kHz Frequency Offset Stop 10.0 MHz<br>or 156.250 MHz                                                           |                      |

| Log Plot                    |                                                                                                                  |                      |

| Noise<br>RMS                | -101.35 dBc/Hz spot Freq 10.0000 kHz<br>0.0022 Rad Lower Limit 10.0000 kHz<br>0.1247 Deg Upper Limit 10.0000 MHz |                      |

| ROPACE RI                   | f file saved                                                                                                     |                      |

Figure 40 : Phase Noise Measurement Fixed DAC value

Next two sets of values for Alpha and Beta were chosen to illustrate the worst and best case phase noise possible in the system. The first measurement shown in Figure 41 represents the worst case phase noise. It has the widest closed-loop bandwidth and significant peaking. Using Equation (8) the peak to peak jitter is 12.84ps RMS. The second measurement shown in Figure 42 represents the best or more common case with more narrow bandwidth and minimal peaking. Its peak to peak jitter is 2.27ps RMS. This is better than the reference source and comparable to the fixed DAC value. It was observed that if the measurement was taken directly at the output of the VCXO the peak to peak jitter is less than 2ps RMS. Therefore it is felt that much of the phase noise present in the measurements is caused by the output and input drivers of the FPGA.

Figure 41 : Phase Noise Measurement Alpha=3;Beta=0

$$PN_{RMS} = \frac{1}{F_{vcxo}} * \frac{1}{360} * RMS_{deg}$$

(8)

| 🔆 Agilent                  | 23:08:39 Feb 19, 2005 T                                                                                                         | Measure              |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Ref -50dBo<br>#Samp<br>Log | c/Hz #Atten 15 dB                                                                                                               | Setup                |

| 10                         |                                                                                                                                 | Measure<br>Log Plot  |

|                            |                                                                                                                                 | Measure<br>Spot Freq |

|                            |                                                                                                                                 |                      |

| 1                          | .0 kHz Frequency Offset Stop 10.0 MHz<br>eq 156.250 MHz                                                                         |                      |

| Log Plot                   |                                                                                                                                 |                      |

| Noise                      | -103.36 dBc/Hz Spot Freq 10.0000 kHz                                                                                            |                      |

| RMS                        | 0.0022         Rad         Lower Limit         10.0000 kHz           0.1279         Deg         Upper Limit         10.0000 MHz |                      |

| No Peak F                  | ายารต์                                                                                                                          |                      |

Figure 42 : Phase Noise Measurement Alpha=0xF;Beta=5

When we compare the measured values of jitter generation to the published papers this ADPLL exceeds the performance of many systems. The integrated ring oscillator based PLL's range from 14.6ps [7] to 15.9ps [8]. Published integrated LC oscillators operating at much higher frequencies range from 3.6ps [8] to 4.77ps [2]. It is expected that the performance of this system would be improved with higher frequencies.

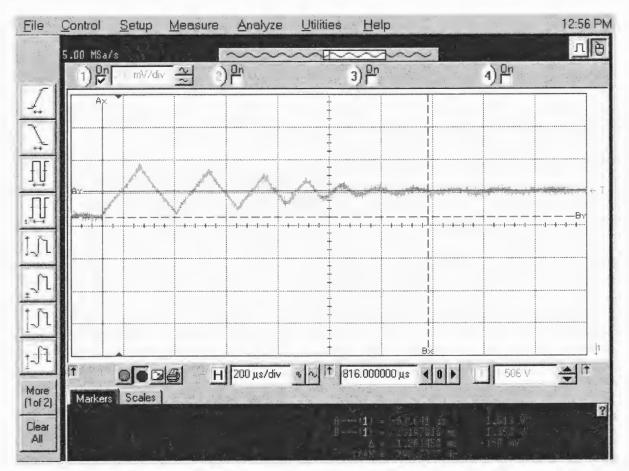

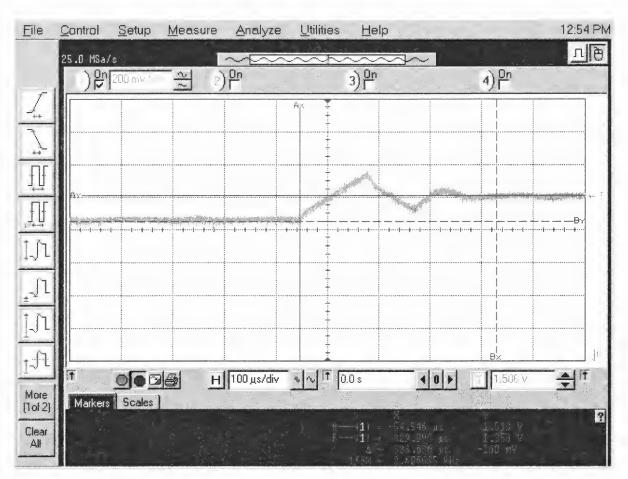

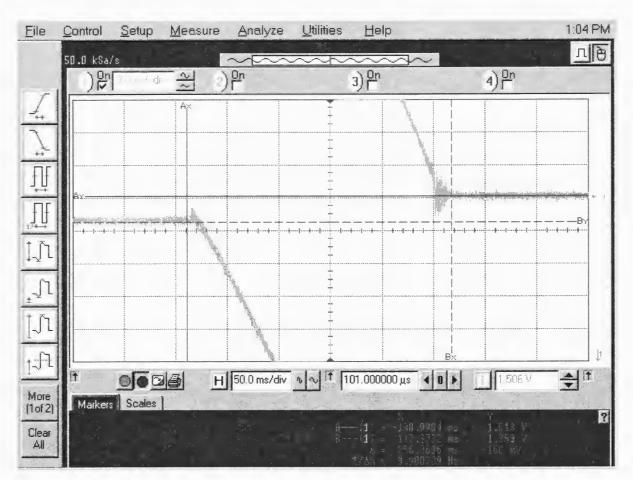

### 3.6 Frequency Step Response

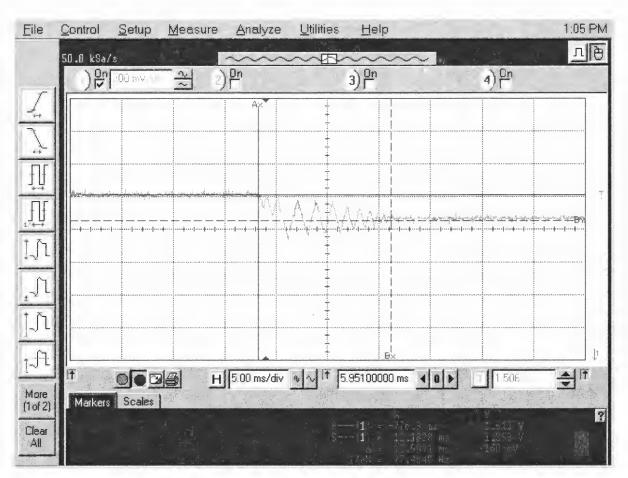

Frequency step response is an important measurement to monitor for PLL's. Test setup #1 was used to generate frequency step responses with different PLL parameter values. The oscilloscope captures are shown in Figure 43 to Figure 46. It should be noted that this is a very large step response and tends to push the ADPLL into non-linear operating points as can be seen by the triangular oscillations in the screen captures. Lee [2] gives a good analysis of this behavior which is caused by slewing. The slewing results because of the maximum rate at which the DAC value can be updated and the behavior of the bang-bang phase detector.

Figure 43 : 1000Hz Frequency Step Response Alpha=6;Beta=3

Figure 44 : 1000Hz Frequency Step Response Alpha=6;Beta=2

It can be seen that lock time increases dramatically when the value of beta is reduced. A smaller value of beta allows the DAC value to be increased faster because the gain of the first order path is much larger. Figure 46 shows an event which results from the large frequency step induced and the very low gain of both first and second order paths. This is not likely to occur in a real system.

Figure 45 : Negative 1000Hz Frequency Step Response Alpha=9;Beta=5

The ADPLL responded by tracking the wrong direction resulting in an out of lock condition. The result is that the DAC value saturates. Eventually the loop forces the DAC value which is a 12 bit unsigned integer value to rollover. The loop then continues to track down until lock is acquired. This event is repeatable and only occurs with a positive step of 1Khz and with large values of Alpha.

Another issue that was observed is that as the value of Alpha is increased, the loop will loose lock momentarily when the value of alpha is changed. This occurs only when alpha is greater than 0x9. This is an issue because the expectation was that the parameters could be modified dynamically in order to produce fast lock times and then increased in order to have lower bandwidths. Changes to beta do not cause the loop to loose lock.

Figure 46 : Positive 1000Hz Frequency Step Response Alpha=9;Beta=5

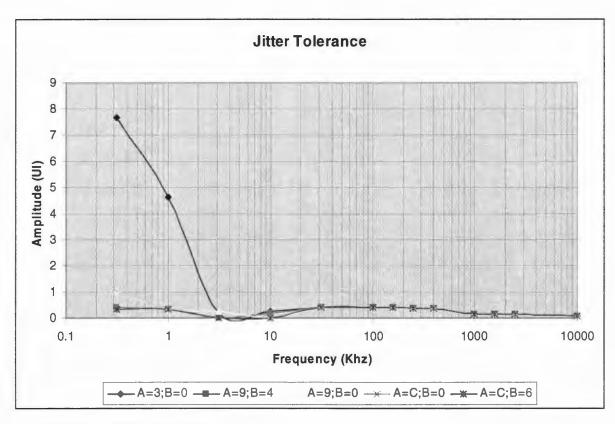

## 3.7 Data Recovery Jitter Tolerance

Jitter tolerance is the ability of a clock and data recovery (CDR) system to receive data with significant amounts of jitter and still be able to accurately recover the data and clock signal. To perform this test, test setup #2 was used to provide a PRBS23 pattern driven into the reference signal input. The output data was monitored for errors and the input data was modulated with sinusoidal jitter. Figure 47 represents the maximum amount of jitter which was used and error free data received. The performance of a CDR system depends on tracking the jitter that is received. Since this system has such low bandwidth it was unable to recover data with greater than 0.39UI of modulation unless the loop bandwidth was significantly higher than the modulation frequency. In fact only the widest bandwidth settings provided adequate jitter tolerance performance. This shows that for acceptable jitter

tolerance performance the bandwidth should be approximately 10x the frequency of the required rolloff point for the required jitter tolerance.

Figure 47 : Jitter Tolerance Plots

#### 3.8 Comparison to Analytical Analysis

Measured phase noise was only slightly larger than the calculated quantization jitter calculated previously. In fact if measured directly at the output of the VCXO it is nearly equal. It was observed that the ADPLL became unstable when the value of Beta approached Alpha within a value of 3. When comparing this with Da Dalt's[3] analysis of minimum Beta we see very good correlation. Consider Table 10 which used a value of D=2 in Equation (4). The measured value column represents the maximum value of Beta where the ADPLL was observed to be stable and able to lock. The second column represents the value of  $\alpha$  as it is used in Da Dalts equations. The third column is the calculated value of  $\beta$  from

DaDalts equations. The fourth column represents the value of Beta which is calculated from the third column. Notice that columns 4 and 5 are consistently different by a value of 2.

|       |          |           | Beta-min   | Measured |

|-------|----------|-----------|------------|----------|

| Alpha | 2^-Alpha | Bmin      | Calculated | Beta-min |

| 7     | 0.007813 | 0.0195313 | 5.68       | 4        |

| 8     | 0.003906 | 0.0097656 | 6.68       | 5        |

| 9     | 0.001953 | 0.0048828 | 7.68       | 6        |

| 10    | 0.000977 | 0.0024414 | 8.68       | 7        |

| 11    | 0.000488 | 0.0012207 | 9.68       | 8        |

Table 10 : Comparison of minimum Beta

According to Da Dalt's [3] equation for optimal value of Beta equation (5), if we specify a value of Alpha equal to 0xC; the optimum value of Beta would be approximately 8. However from Figure 32 we see excessive peaking with any value of Beta greater than 3. However, consider that Da Dalt was examining jitter based on the trajectory and orbit of the closed loop system only. The peaking in the jitter transfer map has a different cause and effect. Therefore a trade-off must be made regarding the effects of the peaking versus effects of larger orbits or less than optimum Beta in order to choose the best performing loop parameters.

#### 3.9 Conclusion

In this chapter data was presented which showed the implemented design operates well with a variety of loop parameter values. Further the ADPLL performs better than published integrated solutions with respect to jitter generation. This is due in no small order to the low noise performance of the crystal based VCXO. Further it is shown that the ADPLL operates effectively as a noise reducing filter and clock multiplying circuit due to the ability to produce very low bandwidth loops.

# **Chapter 4 Conclusion**

In this thesis an all digital PLL based on DAC and VCXO technology was analyzed, designed, and implemented using FPGA technology. The DPLL was characterized with different programmable settings and shown to function well in different applications. As part of the characterization of the ADPLL an automated jitter transfer program was developed to analyze the loop performance. This automation is important in order to produce accurate and repeatable characterization data. The ADPLL was shown to have flexibility in loop bandwidth and was stable across a wide range of parameter settings. The design was shown to operate as both noise filtering, clock multiplying and data recovery applications. The data recovery application's performance was limited by the narrow bandwidth of the implemented design. The performance of the system would benefit with the use of a faster DAC and wider bandwidth. The ADPLL implemented is more suitable for jitter filtering where it was shown to reduce input jitter significantly and have very low jitter generation capability. The Verilog HDL code provided in the thesis can be synthesized to any digital technology using standard industry CAD tools. In this thesis we used a Xilinx Virtex-II ProX FPGA; however the design could be re-processed for the latest Virtex 4 FPGA or designed into an Application Specific Integrated Circuit (ASIC). Additionally, the design is not limited to the particular DAC and VCXO used in this implementation. Most VCXO or VCSO oscillators share the same footprint and pin-out. Therefore, changing operating rate of the design would be straightforward. Further, there exist many DAC's which operate with the same SPI interface as used in this design. Changing the DAC used may require new PCB design due to footprint and pin-out differences between these DAC's. Furthermore, the circuit is not limited to the operation speed of the DAC or digital circuits. It is possible to divide a very high speed VCSO using an external component before entering the FPGA without dramatically affecting performance.

The cost of the implemented design is estimated at less than \$25 which includes the cost of the DAC and VCXO. It is assumed that the FPGA or ASIC would be a pre-existing component which could be expanded to support the added functionality. For comparison purposes, this is a reduction of at least 50% over existing solutions such as Texas Instruments

CDC7005 device and supporting components and over 100% versus existing Integrated Circuit Systems (ICS) devices.

In the thesis an innovative accumulating phase detector was introduced. This phase detector expanded the capabilities of a standard bang-bang phase detector to operate at a higher rate than the loop filter and DAC. This results in a lower update rate for the VCXO however it allows the phase detector to appear more linear than a standard bang-bang phase detector. This reduced rate for the DAC is important because most low cost DAC's have update rates far lower than the clock rates of most digital communication systems today.

## 4.1 Future Work

This thesis introduced an innovative solution for clocking in today's systems. The following is a list of potential future work.

- 1. Characterize the performance benefits of faster DAC.

- 2. Improve Clock and Data Recovery operation.

- 3. Measure low bandwidth performance using equipment capable of measuring in very low frequency band.

- 4. Implement loops with frequencies greater than 600Mhz.

- 5. Design of an automated control system which could dynamically adapt loop parameters.

- 6. Implementation using embedded multipliers of Xilinx Virtex 4.

# Appendix A

## 4.2 Introduction

This Appendix contains the Verilog HDL source code for the implemented design. The function of each of these verilog modules is described in detail in Chapter 2.

## 4.3 Design Top-Level module : fpga\_top.v

```

// FileName: fpga_top.v

//

// Author: Justin Gaither

//

// Begin Date: Tue Nov 30 15:08:16 2004

\parallel

// Description: Top level system for All Digital PLL using external

// DAC and VCXO

//

//

//

Revision History

//

//-----

User Name Full Name

// Date Modified

Descrition of Changes

||

//-----

// $Log: fpga_top.v,v $

// Revision 1.2 2005/01/31 22:10:57 jgaither

// Update for fixed vc, and clk and data to sma

//

// Revision 1.1 2005/01/19 20:26:49 jgaither

// Initial revision

//

//

11

//-----

// NOTES:

//-----

//

11

//-----

`timescale 1ns/100ps

`ifdef TPDA

```

`else `define TPDB #0.1 `define TPDA #0.1 `endif module fpga\_top (/\*AUTOARG\*/ // Outputs SCLK, SDO, SYNC, clk\_sel, clk\_en, dataoutp, dataoutn, clkoutp, clkoutn. // Inputs reset, refclk\_P, refclk\_N, vcoclk\_P, vcoclk\_N ); input reset; input refclk\_P,refclk\_N; input vcoclk\_P,vcoclk\_N; output SCLK.SDO.SYNC; output clk sel,clk en; output dataoutp.dataoutn; output clkoutp.clkoutn; wire [35:0] control0; wire [63:0] sync in; wire [63:0] sync out; wire [3:0] bitsel; clkendac,isync; wire wire [15:0] vc.vcx; wire [8:0] phase error; refsig; reg wire [31:0] integrator; IBUF rst buf (.O(rst) ..I(reset));IBUFGDS refclk buf (.O(refclki), .I(refclk P), .IB(refclk N)); IBUFGDS vcoclk\_buf (.O(vcoclki), .I(vcoclk\_P), .IB(vcoclk\_N)); // BUFG refclk bufg (.O(refclk), .I(refclki)); //BUFG clk bufg (.O(sclk) , .I(sclki)); OBUF clksel buf (.O(clk\_sel), .I(1'b1)); OBUF clken\_buf (.O(clk\_en), .I(1'b0)); OBUFDS data\_buf (.O(dataoutp), .OB(dataoutn), .I(datax)); OBUFDS clk\_buf (.O(clkoutp), .OB(clkoutn), .I(vcoclk));

// Can select divided pdclk or input clock BUFGMUX vcoclk\_bufg (.O(vcoclk), .I0(vcoclki), .I1(pdclk), .S(sync\_out[25])); BUFG vcoclk2\_bufg (.O(vcoclk2), .I(vcoclki));

## vcodiv vcodiv(

| .clkendac | (clkendac),      |

|-----------|------------------|

| .rstent   | (rstcnt),        |

| .bitsel   | (bitsel[3:0]),   |

| .sync     | (isync),         |

| .sclk     | (sclk),          |

| .pdclk    | (pdclk),         |

| // Inputs |                  |

| .clk      | (vcoclk2),       |

| .divent   | (sync_out[63:56] |

| .vcodiv   | (sync_out[23:16] |

| );        |                  |

## pd pd(

| // Outputs   |                |

|--------------|----------------|

| .data        | (datax),       |

| .phase_error | (phase_error), |

| // Inputs    |                |

| .refsig      | (refclki),     |

| .rstcnt      | (rstent),      |

| .vcoclk      | (vcoclk),      |

| .reset       | (rst)          |

| );           |                |

## lp lp(

| // Outputs   |                    |

|--------------|--------------------|

| .VC          | (vc[15:0]),        |

| .integrator  | (integrator),      |

| // Inputs    |                    |

| .clk         | (vcoclk),          |

| .clken       | (clkendac),        |

| .phase_error | (phase_error),     |

| .beta        | (sync_out[55:52]), |

| .alpha       | (sync_out[51:48]), |

| .rstcnt      | (rstent),          |