## **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality  $6^{\circ} \times 9^{\circ}$  black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, Mi 48106-1346 USA 800-521-0600

[]MI

## A re-configurable pipeline ADC architecture with built-in self-test techniques

by

#### Hui Liu

A dissertation submitted to the graduate faculty

in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

Major: Electrical Engineering (Microelectronics)

Program of Study Committee: Marwan M. Hassoun, Co-major Professor William C. Black, Co-major Professor Robert J. Weber Chris Chong-Nuen Chu Yuhong Yang

Iowa State University

Ames, Iowa

2001

Copyright © Hui Liu 2001. All rights reserved.

UMI Number: 3034203

# UMI®

#### UMI Microform 3034203

Copyright 2002 by ProQuest Information and Learning Company. All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

> ProQuest Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

Graduate College

Iowa State University

This is to certify that the doctor's dissertation of

Hui Liu

has met the dissertation requirements of Iowa State University

Signature was redacted for privacy.

#### Co-Major Rrolessor

Signature was redacted for privacy.

#### Co-Major Professor

Signature was redacted for privacy.

#### For the Major Program

# **TABLE OF CONTENTS**

| LIST OF FIGURES                                                   | vi         |

|-------------------------------------------------------------------|------------|

| LIST OF TABLES                                                    | ix         |

| ABSTRACT                                                          | x          |

| 1 INTRODUCTION                                                    | 1          |

| 1.1 Motivation                                                    | 1          |

| 1.2 Dissertation Organization                                     | 3          |

| 2 ON-CHIP ANALOG SIGNAL GENERATION                                | 5          |

| 2.1 Introduction                                                  | 5          |

| 2.2 Bitstream Generation                                          | 5          |

| 2.2.1 Difference between Software and Hardware Generation Methods | 5          |

| 2.2.2 Basic Block Diagram of Generating Optimized Bitstream       | 6          |

| 2.2.3 Bitstream Generator: ΣΔ Modulator                           | 7          |

| 2.2.3.1 Oversampling without Noise Shaping                        | 8          |

| 2.2.3.2 Oversampling with Noise Shaping                           | 11         |

| 2.2.3.3 First Order Sigma-delta Modulator                         | 12         |

| 2.2.3.4 High Order ΣΔ Modulator                                   | 14         |

| 2.2.4 Parameter for the Performance of Bitstream: Length N        | 1 <b>8</b> |

| 2.2.5 Bitstream Optimization                                      | 22         |

| 2.3 Shift Register Ring                                           | 23         |

| 2.4 1-bit DAC                                                     | 24         |

| 2.5 Analog Low Pass Filter                                        | 24         |

| 2.5.1 Specification of LPF                                        | 24         |

| 2.5.2 Power Consideration of the Generated Analog Signal          | 29         |

| 2.6 Multi-phase Signal Generation                                 | 31         |

| 2.7 Chapter Conclusion                                            | 33         |

| 3 ADC TESTING                                                     | 34         |

| 3.1 Introduction                                                  | 34         |

| 3.2 Error Measurements                                            | 34         |

| 3.2.1 Quantization Errors                                         | 35         |

| 3.3 Coherent Sampling [15]                                  |    |

|-------------------------------------------------------------|----|

| 3.4 Linear Histogram Testing                                |    |

| 3.5 Dynamic Histogram Testing                               | 41 |

| 3.6 Chapter Conclusion                                      |    |

| 4 ON-CHIP DYNAMIC TESTING OF ADCs                           | 43 |

| 4.1 Introduction                                            | 43 |

| 4.2 SNR                                                     | 43 |

| 4.2.1 FFT Method                                            |    |

| 4.2.2 Narrow Band Filter Method                             |    |

| 4.2.3 Bias of SNR Estimate via Digital Filter               |    |

| 4.3 Chapter Conclusion                                      |    |

| 5 DESIGN OF RE-CONFIGURABLE PIPELINE ADC                    |    |

| 5.1 Introduction                                            |    |

| 5.2 9-bit 40MHz Pipeline ADC Implementation                 |    |

| 5.2.1 System Specification                                  |    |

| 5.2.2 Multiplying Digital-to-Analog Converter               |    |

| 5.2.3 Operational Amplifier Design                          |    |

| 5.2.3.1 DC Gain                                             |    |

| 5.2.3.2 Bandwidth                                           | 59 |

| 5.2.3.3 Load Capacitance                                    | 60 |

| 5.2.3.4 Gain-boosting OPAMP Design                          | 60 |

| 5.2.3.4.1 Principle of Gain-boosting                        | 60 |

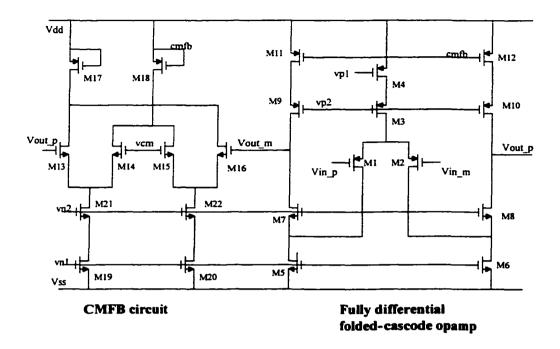

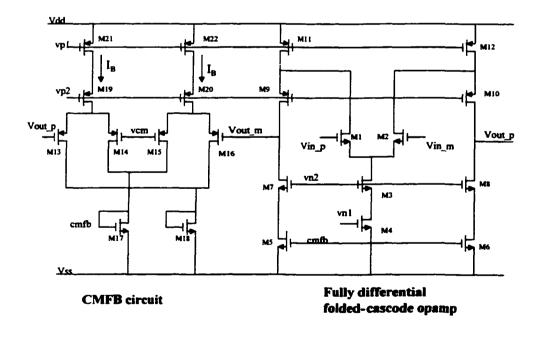

| 5.2.3.4.2 Fully Differential Folded Cascode OPAMP Design    | 63 |

| 5.2.3.4.3 Common-mode Feedback (CMFB) Circuit of Main OPAMP | 64 |

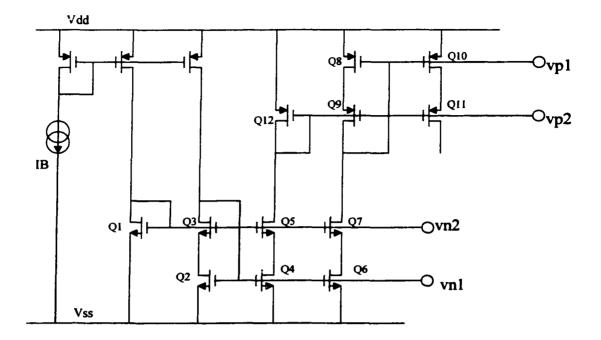

| 5.2.3.4.4 Boosting Amplifier Design                         | 65 |

| 5.2.3.4.5 CMFB for Boosting Amplifier                       | 65 |

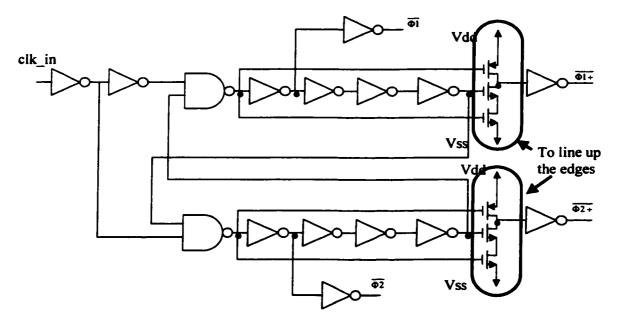

| 5.2.3.4.6 OPAMP Bias Circuit and Clock Generation Circuit   | 69 |

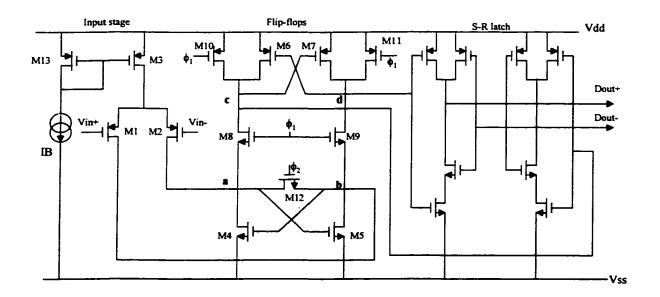

| 5.2.4 Latched Comparator Implementation                     | 71 |

| 5.3 Re-configurable Pipeline Structure                      | 75 |

| 5.3.1 Error Sources in 1-bit-per-stage Pipeline ADC         | 75 |

| 5.3.1.1 Gain Error                                          | 75 |

| 5.3.1.2 Comparator Offset                                   | 76 |

| 5.3.1.3 Charge Injection and Amplifier Offset                    |     |

|------------------------------------------------------------------|-----|

| 5.3.2 Variation between Pipeline Stages                          | 77  |

| 5.3.3 Re-configurable Pipeline ADC                               | 77  |

| 5.3.3.1 4-Switch Re-configuration                                |     |

| 5.3.3.2 8-Switch Re-configuration                                |     |

| 5.3.3.3 Simplified Re-configuration Algorithm                    | 80  |

| 5.3.3.3.1 Grouping Algorithm for 9-bit Pipeline ADC              |     |

| 5.3.3.2 Proof of Grouping Algorithm                              |     |

| 5.3.4 Design Consideration of Re-configurable ADC Cell [38]      |     |

| 5.4 Comparison with other Pipeline ADC Calibration Techniques    |     |

| 5.5 Layout Considerations                                        |     |

| 5.6 Chapter Conclusion                                           |     |

| 6 EXPERIMENTAL RESULTS                                           |     |

| 6.1 Introduction                                                 | 93  |

| 6.2 Experimental Results of Re-configurable Pipeline ADC         |     |

| 6.2.1 PCB Design of Testing Chip                                 | 93  |

| 6.2.2 Testing Setup                                              | 96  |

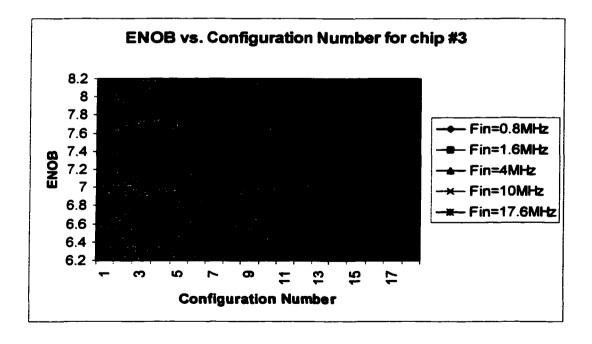

| 6.2.3 Experimental Results                                       | 97  |

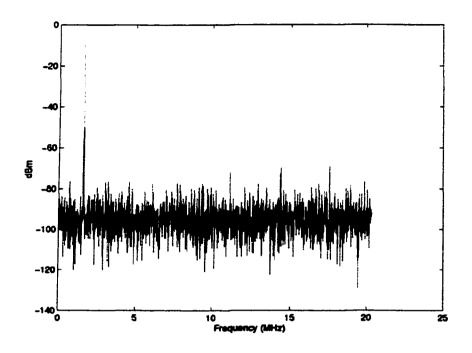

| 6.2.3.1 Dynamic Testing                                          | 97  |

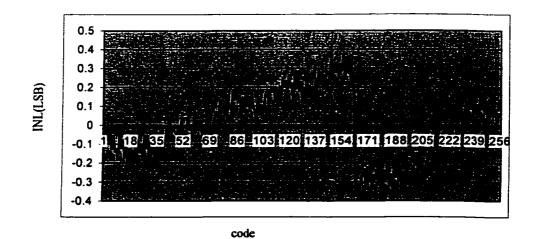

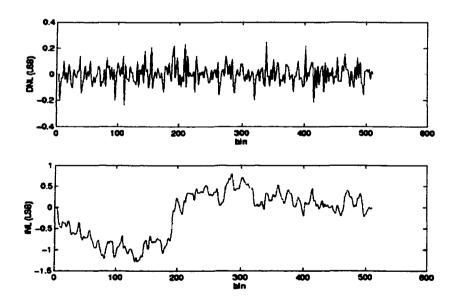

| 6.2.3.2 Static Testing                                           | 98  |

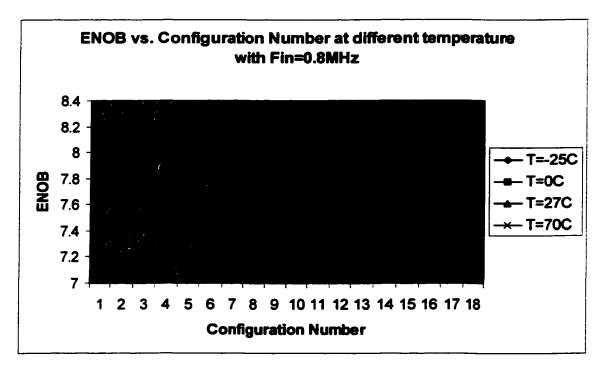

| 6.2.3.3 Temperature Testing                                      |     |

| 6.3 Experimental Results of the on-chip Analog Signal Generation |     |

| 6.4 Chapter Conclusion                                           |     |

| 7 CONCLUSION                                                     |     |

| 7.1 Conclusions                                                  |     |

| 7.2 Recommended Future Work                                      |     |

| REFERENCES                                                       | 114 |

| ACKNOWLEDGEMENTS                                                 | 119 |

|                                                                  |     |

# **LIST OF FIGURES**

| Figure 1.1 Diagram of BIST for pipeline ADC                                                                         | 2  |

|---------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.1 Typical bitstream circuit diagram                                                                        | 7  |

| Figure 2.2 $\Sigma\Delta$ -based digital encoding of a sinusoid                                                     | 8  |

| Figure 2.3 An oversampling system without noise shaping [32]                                                        | 10 |

| Figure 2.4 The linear model of the modulator                                                                        | 11 |

| Figure 2.5 First order sigma-delta modulator                                                                        | 12 |

| Figure 2.6 Second-order ΣΔ modulator                                                                                | 14 |

| Figure 2.7 Third-order $\Sigma\Delta$ modulator                                                                     | 15 |

| Figure 2.8 Cascade-of-integrators structure used to realize the 5 <sup>th</sup> -order modulator                    | 16 |

| Figure 2.9 Frequency response of a long bitstream: length=2 <sup>16</sup> (Matlab <sup>TM</sup> simulation result)  | 19 |

| Figure 2.10 Frequency response of a short bitstream, length=2 <sup>10</sup> (Matlab <sup>™</sup> simulation result) | 19 |

| Figure 2.11 SNR vs. bitstream position                                                                              | 23 |

| Figure 2.12 7 <sup>th</sup> order sigma-delta modulator frequency response                                          | 25 |

| Figure 2.13 7 <sup>th</sup> order modulator followed by 7 <sup>th</sup> order Butterworth LPF,                      |    |

| SNR=98.1132dB, ENOB=16.0055                                                                                         |    |

| Figure 2.14 7th order modulator plus 4th order LPF, SNR=75.8411dB, ENOB=12.3058                                     | 26 |

| Figure 2.15 The same modulator followed by a $2^{nd}$ order modulator, SNR=43.0123,                                 |    |

| ENOB=6.8525                                                                                                         | 27 |

| Figure 2.16 7 <sup>th</sup> order vs. 2 <sup>nd</sup> order modulator frequency response                            | 28 |

| Figure 2.17 Filter off-chip scheme                                                                                  | 29 |

| Figure 2.18 Power for the input and output of the $\Sigma\Delta$ modulator ( $\omega_x$ is the analog testing       |    |

| signal generated by the $\Sigma\Delta$ modulator)                                                                   | 30 |

| Figure 2.19 Diagram of multi-phase signal generation.                                                               | 32 |

| Figure 2.20 Generated multi-phase signals                                                                           | 32 |

| Figure 3.1 ADC transfer curve                                                                                       | 34 |

| Figure 3.2 Spectrum of ideal 6bit ADC with N=1024, M=24, where noise floor is not correct                           | 38 |

| Figure 3.3 Spectrum of ideal 6bit ADC with N=1024, M=23                                                             | 38 |

| Figure 3.4 The INL of an 8-bit ADC                                                                                  | 40 |

| Figure 3.5 The DNL of a 8-bit ADC                                                                                   | 40 |

| Figure 3.6 Spectrum of 6-bit ADC obtained with relatively prime M                                     | 41         |

|-------------------------------------------------------------------------------------------------------|------------|

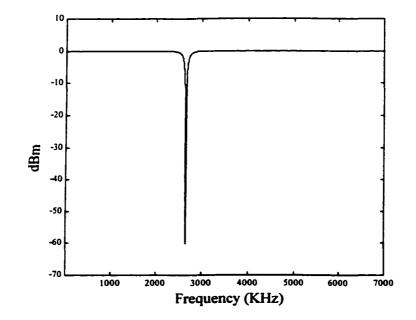

| Figure 4.1 Digital narrow band filter (NBF) [18]                                                      | 45         |

| Figure 4.2 The frequency response $ H_{bp}(f) $ of the bandpass output of the                         | 48         |

| Figure 4.3 The FFT of the bandpass output of the narrow-band digital filter                           | 49         |

| Figure 4.4 The FFT of the notch output of the narrow-band digital filter                              | 49         |

| Figure 4.5 The frequency response $ H_{nt}(f) $ of the notch output of the narrow-band digital filter | er 50      |

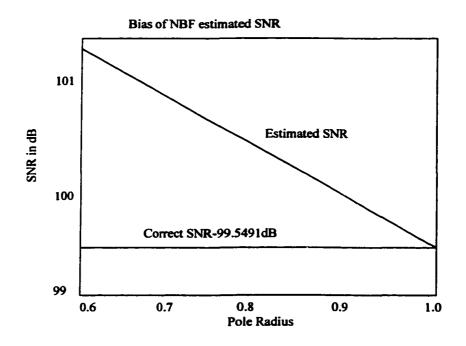

| Figure 4.6 Bias of estimated SNR vs. pole radius                                                      | 50         |

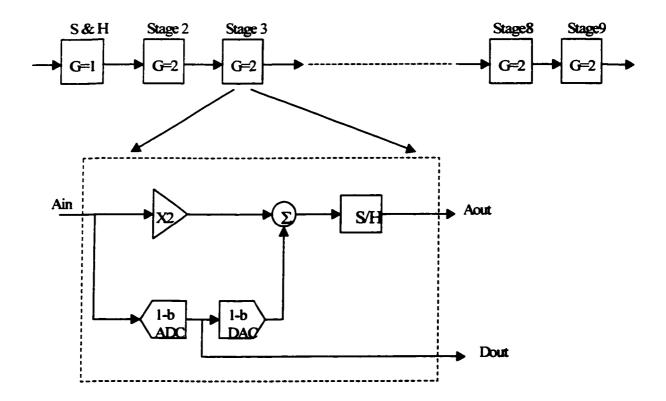

| Figure 5.1 The general architecture of pipeline ADC                                                   | 53         |

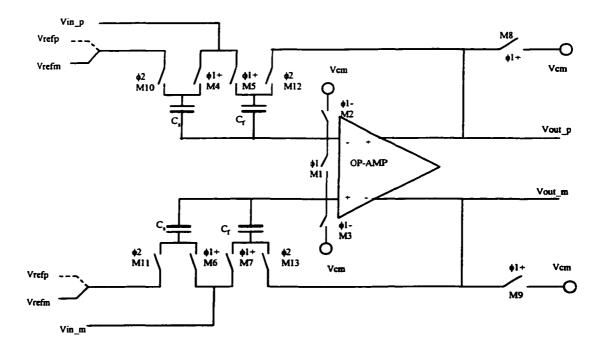

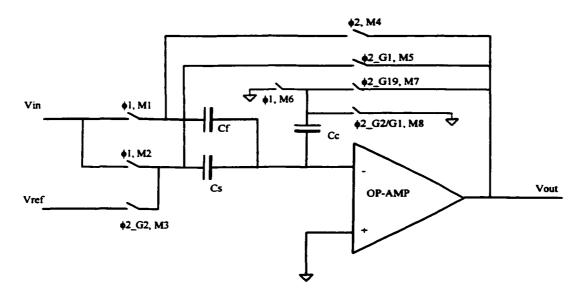

| Figure 5.2 Fully Differential Multiplying Digital-to-Analog Converter                                 | 55         |

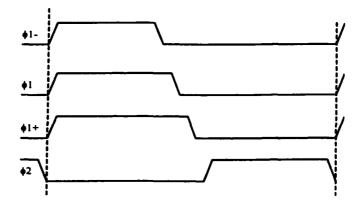

| Figure 5.3 Timing Diagram                                                                             | 55         |

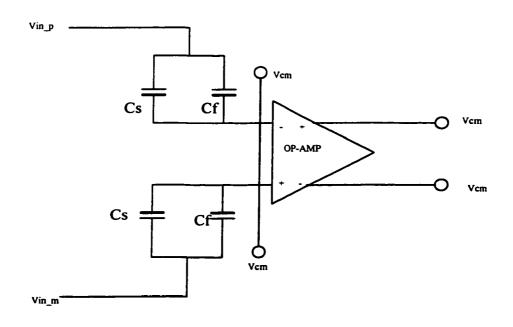

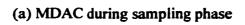

| Figure 5.4 MDAC during different clock phase                                                          | 56         |

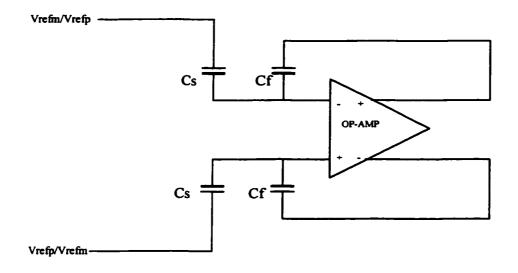

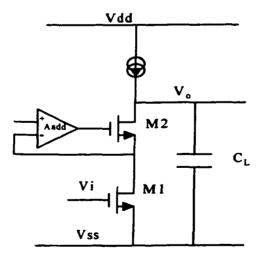

| Figure 5.5 Gain circuit using an opamp                                                                | 59         |

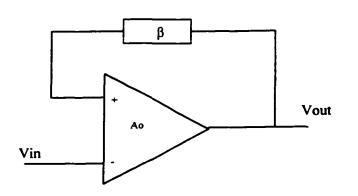

| Figure 5.6 Main operational opamp with boosting amplifier                                             | 62         |

| Figure 5.7 Cascode gain stage with gain enhancement                                                   | 62         |

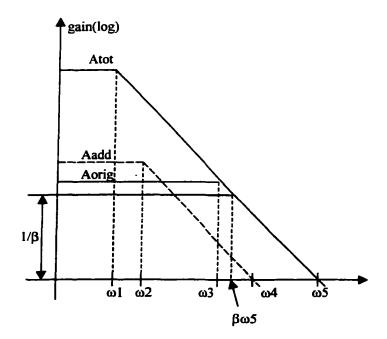

| Figure 5.8 Bode plots of the original, additional and improved gain stage                             | 63         |

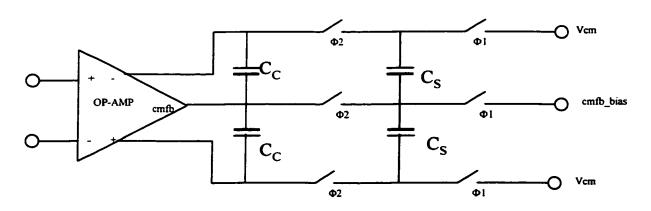

| Figure 5.9 Common mode feedback circuit                                                               | 65         |

| Figure 5.10 Boosting-n amplifier with CMFB circuit                                                    | 66         |

| Figure 5.11 Boosting-p amplifier with CMFB circuit                                                    | 66         |

| Figure 5.12 Opamp bias circuit                                                                        | 69         |

| Figure 5.13 Clock generation circuit                                                                  | 70         |

| Figure 5.14 Schematic of the CMOS comparator                                                          | 71         |

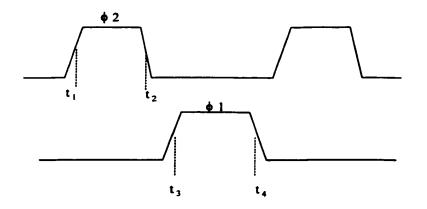

| Figure 5.15 Timing diagram                                                                            | 72         |

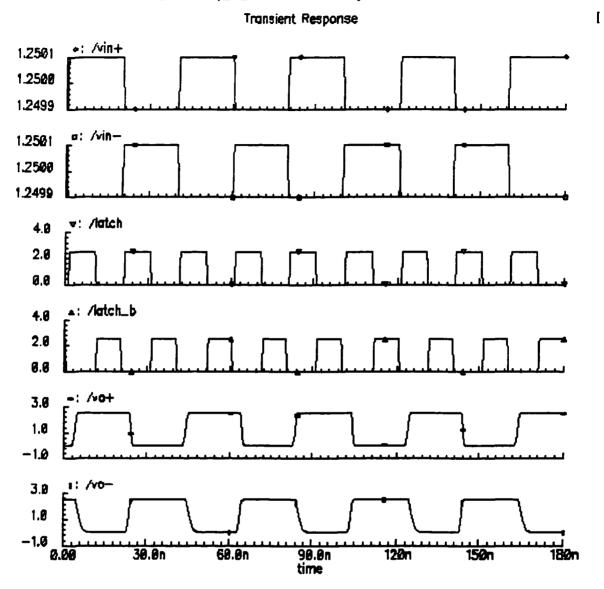

| Figure 5.16 The transient analysis of comparator                                                      | 74         |

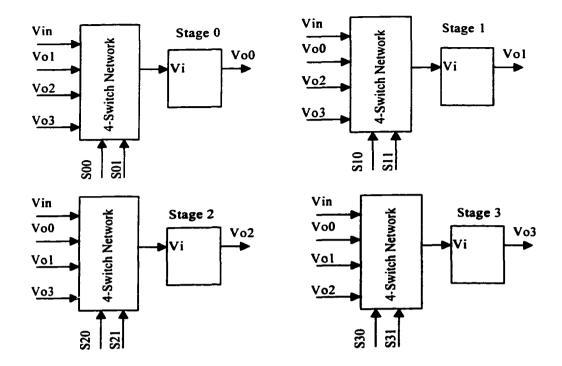

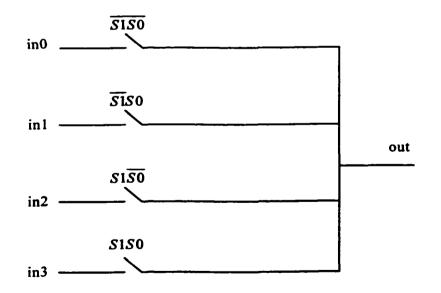

| Figure 5.17 4-tages of pipeline with re-configuration ability using 4-switch network                  | <b>79</b>  |

| Figure 5.18 4-Switch network                                                                          | <b>79</b>  |

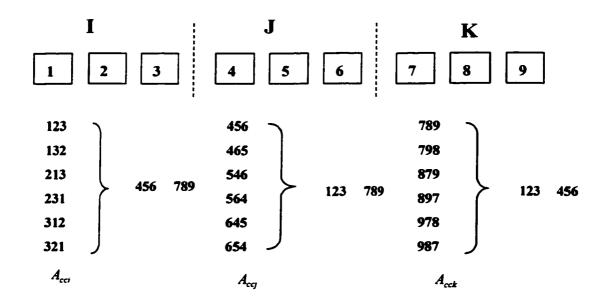

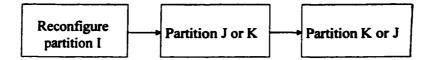

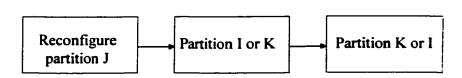

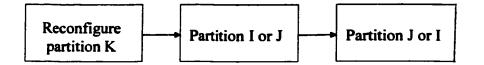

| Figure 5.19 The grouping method of a 9-stage ADC                                                      | 81         |

| Figure 5.20 The first six measurements                                                                | 81         |

| Figure 5.21 The second six measurements                                                               | 82         |

| Figure 5.22 The last six measurements                                                                 | 82         |

| Figure 5.23 Giain-of-1/gain-of-2/gain-of-1.9 Multiplying Digital-to-Analog Converter                  | <b>8</b> 6 |

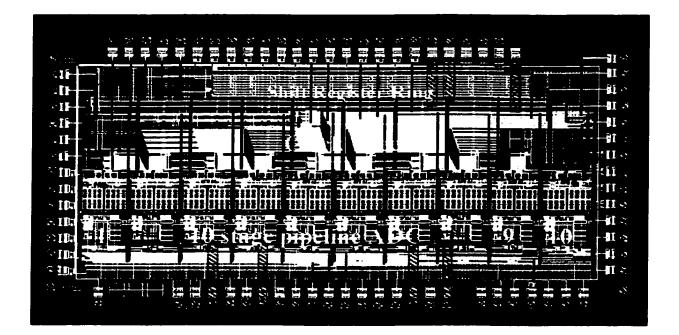

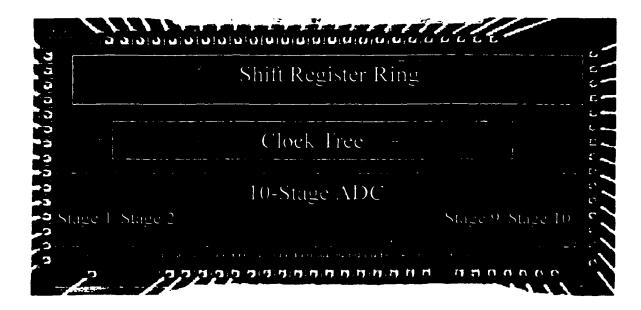

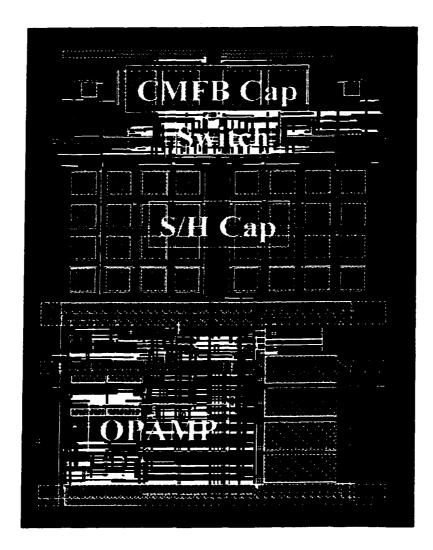

| Figure 5.24 The layout of the chip                                                                    | 89         |

| Figure 5.25 Die photo                                                                                 | 90         |

|                                                                                                       |            |

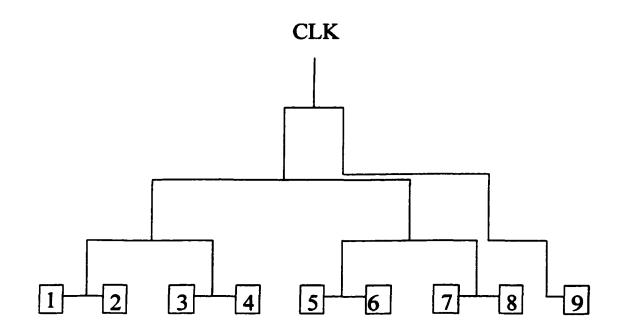

| Figure 5.26 The floor plan of clock tree for stage 1 through stage 990                    |

|-------------------------------------------------------------------------------------------|

| Figure 5.27 The layout of one stage of ADC91                                              |

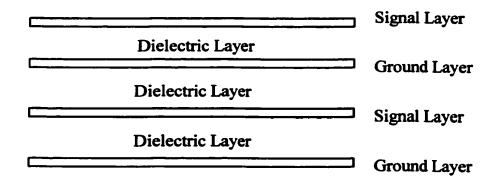

| Figure 6.1 Cross-section of 4-layer PCB93                                                 |

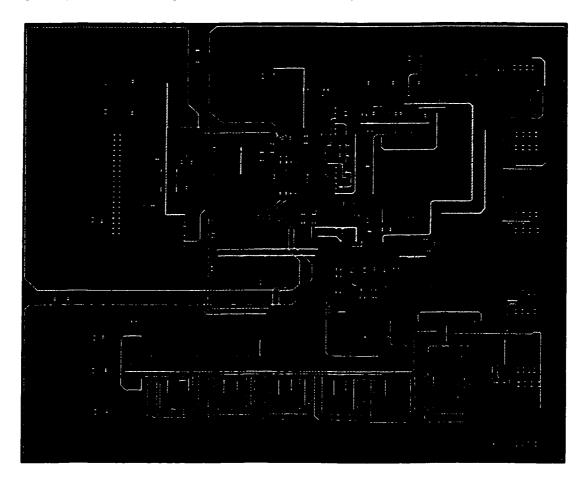

| Figure 6.2 The layout of PCB94                                                            |

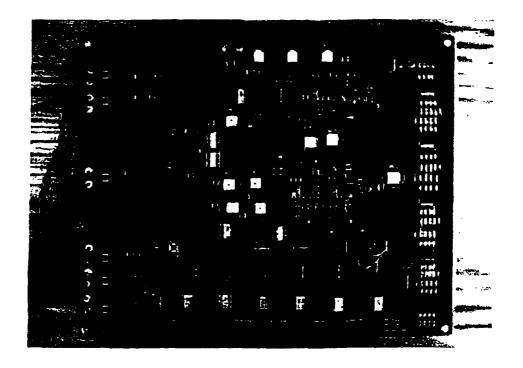

| Figure 6.3 Photo of PCB95                                                                 |

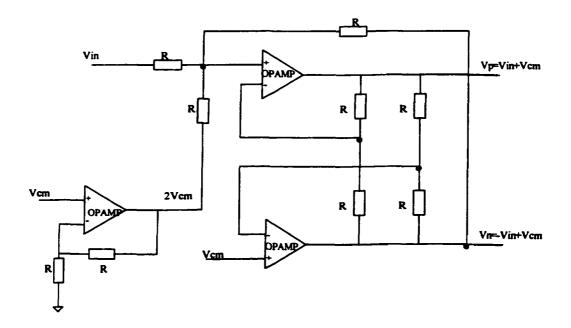

| Figure 6.4 The single-to-differential circuit for LF testing95                            |

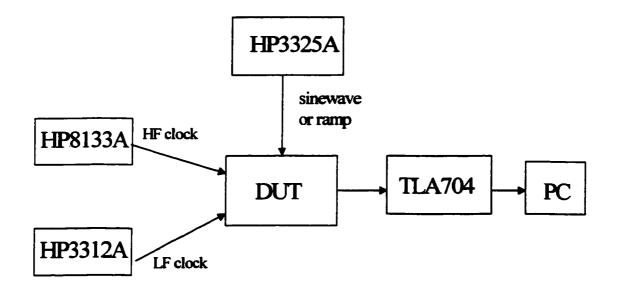

| Figure 6.5 Setup of testing                                                               |

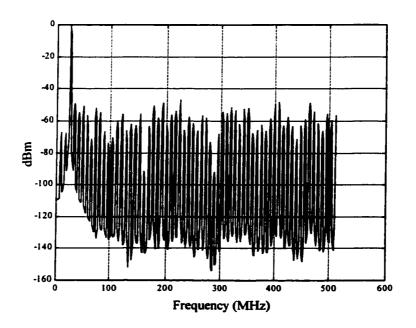

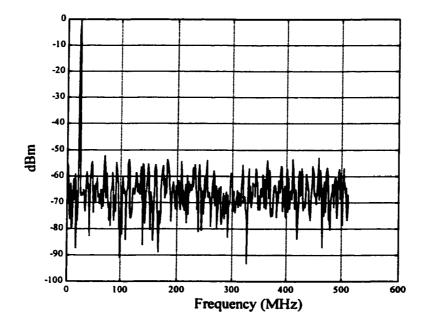

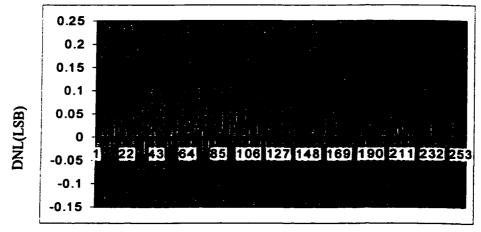

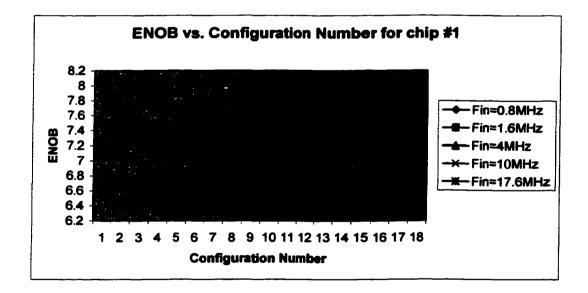

| Figure 6.6 The testing results of chip #1 at normal temperature and Fclk=40MHz98          |

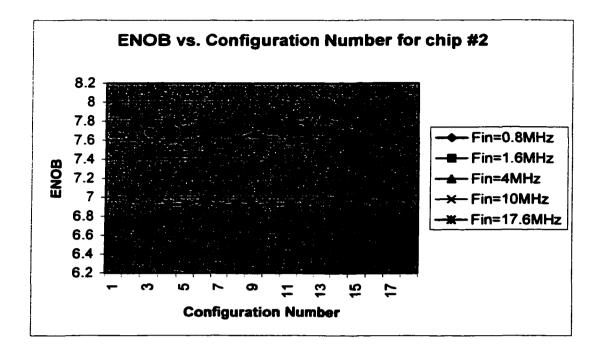

| Figure 6.7 The testing results of chip #2 at normal temperature and Fclk=40MHz99          |

| Figure 6.8 The testing results of chip #3 at normal temperature and Fclk=40MHz            |

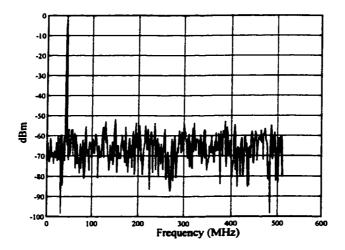

| Figure 6.9 Typical plot of FFT of output of ADC (Chip #2, Configuration No.9)             |

| Figure 6.10 The static test of re-configurable ADC (Chip #2, Configuration No.9)          |

| Figure 6.11 The temperature testing results of chip #2 with Fin=0.8MHz and Fclk=40MHz 101 |

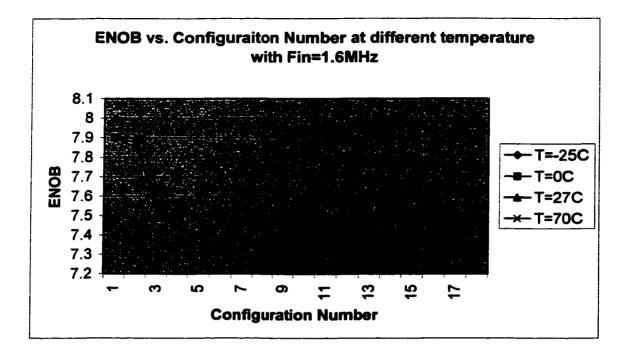

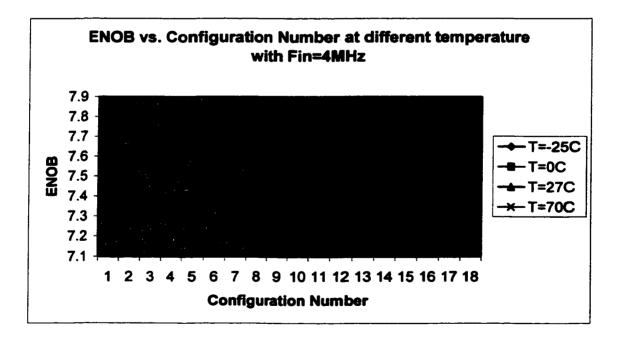

| Figure 6.12 The temperature testing results of chip #2 with Fin=1.6MHz and Fclk=40MHz 102 |

| Figure 6.13 The temperature testing results of chip #2 with Fin=4.0MHz and Fclk=40MHz     |

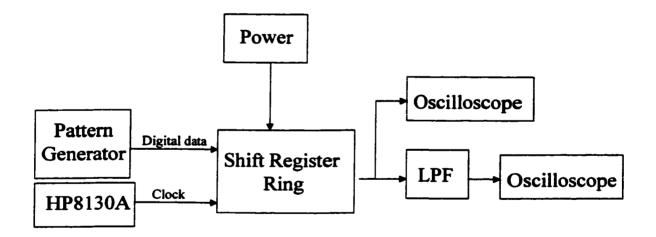

| Figure 6.14 The setup of testing on-chip analog signal generator                          |

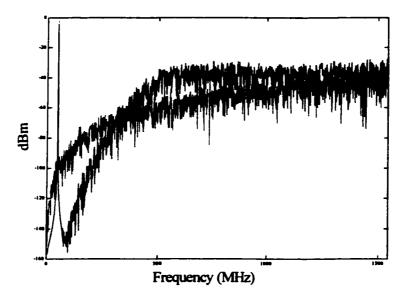

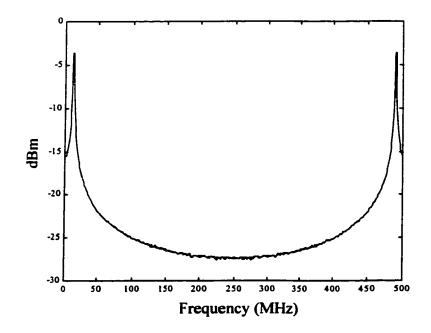

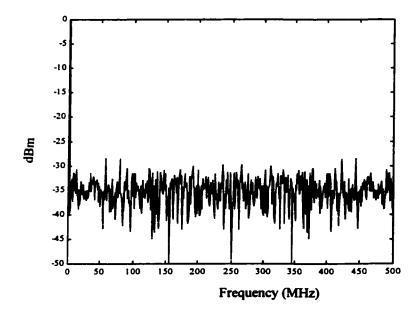

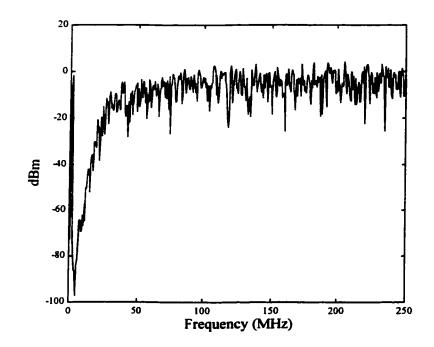

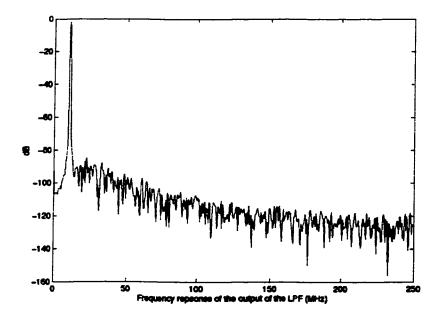

| Figure 6.15 The frequency response of the output of the shift register ring               |

| Figure 6.16 The frequency response of the output of the LPF                               |

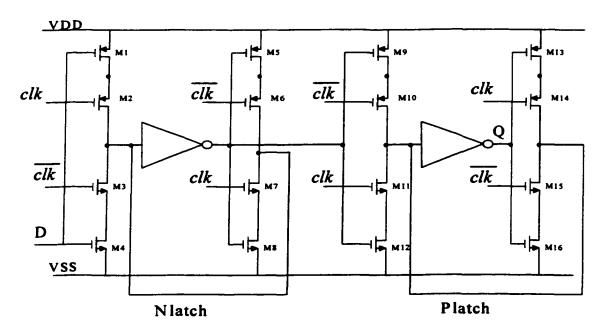

| Figure 6.17 The schematic of DFF105                                                       |

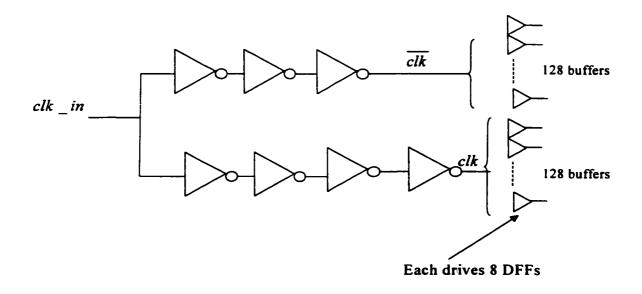

| Figure 6.18 The clock tree buffer used for 1024-shift register                            |

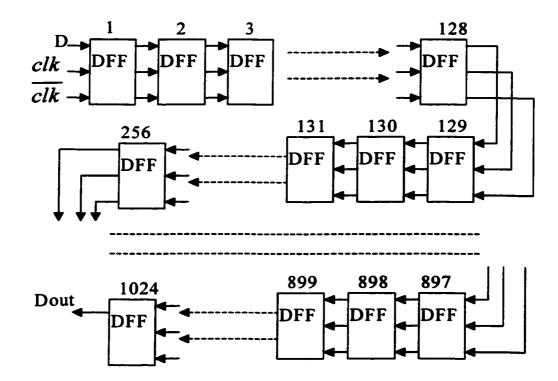

| Figure 6.19 The floor plan of 1024-shift register                                         |

| Figure 6.20 The measured output of the shift register ring                                |

| Figure 6.21 The zoomed in layout of the error108                                          |

| Figure 6.22 The zoomed in micrograph of the error                                         |

# LIST OF TABLES

| Table 5.1 | The specification of main opamp with 2pF load plus switch | 64 |

|-----------|-----------------------------------------------------------|----|

| Table 5.2 | The specification of boost_p with 1pF load                | 67 |

| Table 5.3 | The specification of boost_n with 1pF load                | 67 |

| Table 5.4 | The specification of gain-boosted opamp with 2pF load     | 68 |

| Table 5.5 | Specification of the latched comparator                   | 73 |

| Table 5.6 | Proof of the grouping algorithm                           |    |

| Table 5.7 | Comparison with the other calibration techniques          |    |

| Table 6.1 | Configurations of re-configurable pipeline ADC            | 97 |

## ABSTRACT

High-performance analog and mixed-signal integrated circuits are integral parts of today's and future networking and communication systems. The main challenge facing the semiconductor industry is the ability to economically produce these analog ICs. This translates, in part, into the need to efficiently evaluate the performance of such ICs during manufacturing (production testing) and to come up with dynamic architectures that enable the performance of these ICs to be maximized during manufacturing and later when they're operating in the field. On the performance evaluation side, this dissertation deals with the concept of Built-In-Self-Test (BIST) to allow the efficient and economical evaluation of certain classes of high-performance analog circuits. On the dynamic architecture side, this dissertation deals with pipeline ADCs and the use of BIST to dynamically, during production testing or in the field, re-configure them to produce better performing ICs.

In the BIST system proposed, the analog test signal is generated on-chip by sigma-delta modulation techniques. The performance of the ADC is measured on-chip by a digital narrow-band filter. When this system is used on the wafer level, significant testing time and thus testing cost can be saved.

A re-configurable pipeline ADC architecture to improve the dynamic performance is proposed. Based on dynamic performance measurements, the best performance configuration is chosen from a collection of possible pipeline configurations. This basic algorithm can be applied to many pipeline analog systems. The proposed grouping algorithm cuts down the number of evaluation permutation from thousands to 18 for a 9-bit ADC thus allowing the method to be used in "real" applications.

To validate the developments of this dissertation, a 40MS/s 9-bit re-configurable pipeline ADC was designed and implemented in TSMC's 0.25µm single-poly CMOS digital process. This includes a fully differential folded-cascode gain-boosting operational amplifier with high gain and high unity-

gain bandwidth. The experimental results strongly support the effectiveness of re-configuration algorithm, which provides an average of 0.5bit ENOB improvement among the set of configurations. For many applications, this is a very significant performance improvement.

The BIST and re-configurability techniques proposed are not limited to pipeline ADCs only. The BIST methodology is applicable to many analog systems and the re-configurability is applicable to any analog pipeline system.

## **1 INTRODUCTION**

#### **1.1 Motivation**

Rapid growth in the area of wireless communication has increased the demand for high performance integrated circuits. Testing of these circuits represents a challenge. Yet built-in self-test (BIST) is an efficient way to save testing time and cut testing cost. While the concept of BIST has been in use for more than half a century, BIST implemented in pipeline Analog-to-Digital Converter (ADC) has become popular only during the past decade. Today, there are still many interesting topics that deal with BIST applications.

High-performance digital communication requires ADCs with resolutions of at least 7-bits and sampling rates higher than 40Msample/s. In the past decade, the pipeline ADC architecture has become suitable for such applications because it can be insensitive to offsets in comparators and operational amplifiers by using redundancy and digital correction. However, traditional designs of pipeline ADCs have relied on high-gain operational amplifiers and excellent capacitor matching to produce high-performance converters. Such analog components are becoming more difficult to design in scaled technologies because of the reduced power-supply voltages. How to improve the ADC's performance is the major task of designers in this area.

The motivation of this Ph.D work is to explore system level as well as circuit level design techniques for improving the performance of pipeline ADCs and to explore the BIST application in pipeline ADCs. A prototype chip was implemented and tested to demonstrate proposed architecture.

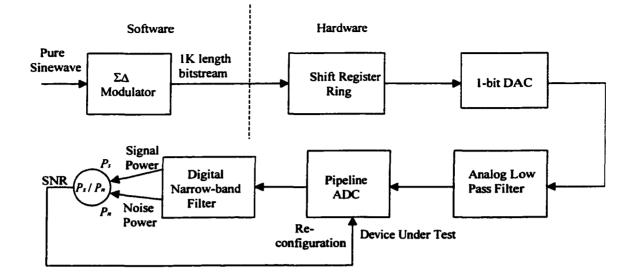

Figure 1.1 shows the proposed diagram of a re-configurable pipeline ADC architecture with builtin self-test technique. It is composed of two major parts: a software part and a hardware part. The software uses a  $\Sigma\Delta$  modulator to generate on-chip analog signal, which appears as a bitstream. This

Figure 1.1 Diagram of BIST for pipeline ADC

bitstream is stored using a shift register. By repeating the bitstream, a signal source is emulated onchip. This signal source is always ON during the test procedure. As an example, consider a bitstream of length 1K. This 1K bitstream goes through a 1-bit DAC to generate an analog signal, which is in 1bit format. However this 1bit bitstream is noise-shaped: noise is pushed to high frequency range. By using an analog low-pass filter (LPF), the high frequency range noise is filtered out. The output of the analog LPF is the real analog testing signal that is needed for testing the pipeline ADC, which is the device under test (DUT). The performance of the ADC will be measured by the digital narrow band filter (NBF), which will measure the signal to noise ratio (SNR). According to the measurement results, a re-configuration algorithm is applied on the re-configurable pipeline ADC to improve the ADC's performance.

The key contributions of this Ph.D work are:

1) A BIST system for re-configurable pipeline ADCs is proposed. It is a unique system with analog input testing signal generated on-chip as well as the dynamic performance of the ADC measured on-chip. When this system is used in wafer test, it will save testing time and thus testing costs.

- 2) A re-configurable pipeline ADC architecture to improve the dynamic performance is proposed. Based on the dynamic performance measurements, the best performance configuration is chosen from a collection of possible pipeline configurations. This basic algorithm can be applied to many pipeline analog systems.

- 3) The grouping algorithm for re-configurable pipeline ADCs is proposed. It can cut down the number of evaluation permutation from thousands to 18 for a 9-bit ADC thus allowing the method to be used in "real" applications.

- 4) A 40Msample/s 9-bit re-configurable pipeline ADC is designed and implemented in TSMC's 0.25µm single-poly CMOS digital process. It includes a fully differential folded-cascode gainboosting operational amplifier with high gain and high unity gain bandwidth.

- 5) Verification of the prototype under different temperature conditions, with the experimental results strongly supporting the effectiveness of the re-configuration algorithm. It provides an average of 0.5bit ENOB improvement among the set of configurations.

#### **1.2 Dissertation Organization**

In chapter 2, the principles of on-chip analog signal generation are introduced. The underlying principles of  $\Sigma\Delta$  modulators are described, with the simulation results shown. This part is the software part as shown in Figure 1.1. Matlab<sup>TM</sup> is used for simulation.

Chapter 3 concentrates on the basic principles of ADC testing, including static testing and dynamic testing. Testing principles such as Coherent sampling and histogram testing methods are described. Those testing methods will be used on the prototype chip testing.

In chapter 4, the on-chip dynamic performance measurement scheme is described. The focus is on the principle of Narrow-Band Filter (NBF). This method is used in BIST instead of traditional industry Fast Fourier Transform (FFT) method, which is difficult to be implemented on-chip.

Chapter 5 focuses on the design of the re-configurable pipeline ADC. Design principles of each component in pipeline ADC are presented. The re-configuration grouping algorithm is proposed, and the re-configurable pipeline ADC architecture is described.

The experimental results of the prototype chip are given in chapter 6. The testing procedures are described. Testing results in different testing temperatures are presented. Experimental results validate that the proposed re-configuration algorithm provides an average of 0.5bit ENOB improvement among the set of configurations.

Finally the conclusion of this work is presented in chapter 7.

# **2 ON-CHIP ANALOG SIGNAL GENERATION**

#### **2.1 Introduction**

An important component of a mixed-signal BIST is a precision analog signal generator. In this chapter, the concept of on-chip analog signal generation is introduced. The basic diagram of a bitstream generator is presented, and the parameters for the performance of the bitstream are discussed. Finally the optimization of the bitstream is covered. Simulation results are shown for each part. In this dissertation, a technique to generate sinewaves with small die area and simple circuits is carried out. By using some memory on the IC, the output of a sigma-delta ( $\Sigma\Delta$ ) modulator can be periodically reproduced [1]. First, the difference between software and hardware generation methods is discussed. Then, the basic block diagram to generate an optimized bitstream is introduced. Finally, the method to encode the analog signals into a 1-bit pattern for digital storage is explained.

#### **2.2 Bitstream Generation**

#### 2.2.1 Difference between Software and Hardware Generation Methods

Bitstream generation can be done in two ways. The first approach uses analog circuits, such as Colpitts or Wien-Bridge oscillators [1]. However, in a mixed-signal test strategy, the test circuits should themselves be testable. This makes testing these circuits difficult. The second approach is to use a digital signal generator and convert the signal with a digital-to-analog converter (DAC) [2]. Digital generators do not require calibration and are easily testable using standard digital test techniques. But, traditional memory-based generators, such as direct digital frequency synthesis (DDFS), require large areas. What is significant is that these schemes require the use of a multi-bit DAC, which is highly susceptible to process variations and requires rigorous testing.

In this dissertation, a different method to generate the bitstream: recording a short portion of the output of a sigma-delta oscillator and reproducing it periodically [5]. This is a software generation method. Compare with the two traditional hardware generation methods discussed above, there are two main differences between them: complexity and stability.

First, let us think about the order of modulator. Increasing the order of the modulator means increased complexity when the modulator is realized in hardware. However, if realized via software, an increase in order does not increase the complexity of the generation and high-order modulators can be implemented efficiently. In this dissertation, the analog signal is generated for testing the pipeline ADC. If the ADC has N-bit resolution, then the analog input signal for on-chip simulation should be at least N+2-bit accuracy. The high accuracy of the analog input signal can be guaranteed fulfilled using software without increasing any on-chip hardware.

Second, let us consider stability. The software generation implementation does not necessarily have to be stable in the classical sense, it only needs to be stable long enough to acquire a sufficient number of points to create a bitstream.

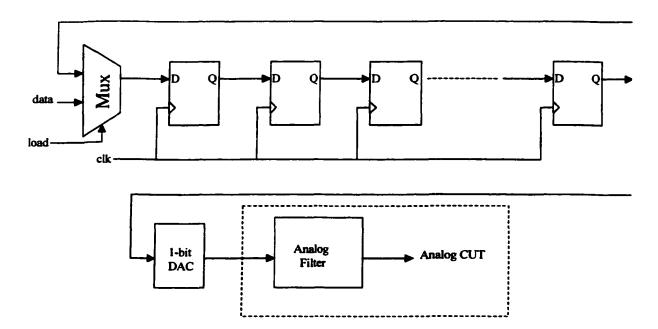

#### 2.2.2 Basic Block Diagram of Generating Optimized Bitstream

The basic circuit to generate the bitstream is very simple: a 1-bit shift register with the output fed back to the input, a 1-bit DAC, and an analog filter. A block diagram of a typical circuit is shown in Figure 2.1 [4] [5] [7].

Now, let us see how to encode an analog signal into a 1-bit bitstream pattern. The pattern is labeled "data" in Figure 2.1.

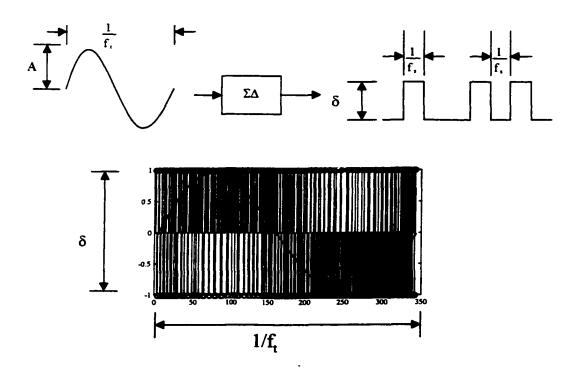

#### 2.2.3 Bitstream Generator: 5 Modulator

A  $\Sigma\Delta$  modulator is used to transfer an analog signal into a 1-bit bitstream. For a  $\Sigma\Delta$  DAC, the signal conversion is performed by encoding a multi-bit digital input signal into a single-bit stream with a peak-to-peak amplitude of  $\Delta$  using digital signal processing and over-sampling techniques [5]. Figure 2.2 shows this process. It applies to a sinusoidal digital input signal of amplitude A and frequency  $f_t$  that has been greatly over-sampled (i.e.,  $f_s >> f_t$ ). We can see from Figure 2.2, the output toggles between the high and low state in such a way that the input signal is encoded into the density of the output waveform. Such a signal is known as a pulse-density modulated (PDM) signal. The difference between the output bit pattern and the input signal is denoted as quantization error. It is noted that the input multi-bit digital signal can be recovered quite simply by digitally filtering the 1-bit output. This is because the  $\Sigma\Delta$  encoding process ensures that the input signal and the quantization error, occupy different frequency regions.

Figure 2.1 Typical bitstream circuit diagram

Figure 2.2  $\Sigma\Delta$ -based digital encoding of a sinusoid

To transform the digital input signal into analog form, the serial stream is simply filtered using an analog filter with bandwidth  $f_B$ , which is greater than  $f_r$  (as shown in Figure 2.2). While the filtering operation will eliminate most of the quantization noise, it will not eliminate all of it; some noise lies in-band and cannot be separated from the signal by filtering. It will be shown later in this chapter with simulation results.

There are different kinds of  $\Sigma\Delta$  modulators, which mean different PDMs or noise shaping for the bitstream. The next section will explore some of them.

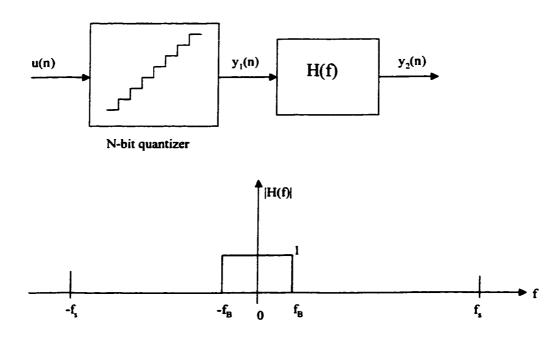

#### 2.2.3.1 Oversampling without Noise Shaping

Quantization introduces distortion. If we assume the error has statistical properties that are independent of the signal, then the error can be represented as noise. Let  $\Delta$  be the quantization level

spacing. When we treat the quantization error e as having equal probability of lying anywhere in the range  $\pm \Delta/2$ , its mean square value is given by [8]

$$e_{rms}^{2} = \frac{1}{\Delta} \int_{\sqrt{2}}^{\sqrt{2}} e^{2} de = \frac{\Delta^{2}}{12}$$

(2.1)

Oversampling occurs when the signals of interest are bandlimited to  $f_B$  while the sampling rate is at  $f_s$ , where  $f_s > 2f_B$ . The oversampling ratio (OSR) is defined as

$$OSR = \frac{f_s}{2f_B}$$

(2.2)

Assuming the quantization noise is white, and noting that the total noise power is  $e_{max}^2$  in the range of  $\pm \frac{f_s}{2}$ , the spectral density of the quantization noise is

$$E(f) = e_{rms} \sqrt{\frac{1}{f_s}} = \left(\frac{\Delta}{\sqrt{12}}\right) \sqrt{\frac{1}{f_s}}$$

(2.3)

As shown in Figure 2.3, after quantization, since the signals of interest are all below  $f_B$ ,  $y_1(n)$  is filtered by H(f) to create the signal  $y_2(n)$ . This filter eliminates quantization noise (together with any other signals) greater than  $f_B$ . Then the noise power  $P_n$  that falls into the signal band will be given by

$$P_{n} = \int_{f_{a}}^{f_{a}} E^{2}(f) df = e_{rms}^{2} \left( 2f_{B}T \right) = \frac{e_{rms}^{2}}{OSR} = \frac{\Delta^{2}}{12} \frac{1}{(OSR)}$$

(2.4)

Assuming the input signal is a sinusoidal wave, and N-bit quantizer is used, its maximum peak value without clipping is  $2^{N}(\Delta/2)$ . For this maximum sinusoidal wave, the signal power, P<sub>s</sub>, is given by

$$P_{s} = \left(\frac{\Delta 2^{N}}{2\sqrt{2}}\right)^{2} = \frac{\Delta^{2} 2^{2N}}{8}$$

(2.5)

Figure 2.3 An oversampling system without noise shaping [32]

The signal power will not change after oversampling and low pass filtering H(f) because the assumption is that the signal's frequency content is below  $f_B$ .

From equation (2.4) and (2.5), we can calculate the maximum SNR (in dB) to be the ratio of the maximum sinusoidal power to the quantization noise:

$$SNR_{\max} = 10\log\left(\frac{P_s}{P_n}\right) = 10\log\left(\frac{3}{2}2^{2N}\right) + 10\log(OSR)$$

(2.6)

which is also equal to

$$SNR_{max} = 6.02N + 1.76 + 10 \log(OSR)$$

(2.7)

The first term is the SNR due to the N-bit quantizer while the OSR term is the SNR enhancement obtained from oversampling. Each doubling of the sampling frequency will decrease the in-band noise by 3dB, increasing the resolution by half a bit.

#### 2.2.3.2 Oversampling with Noise Shaping

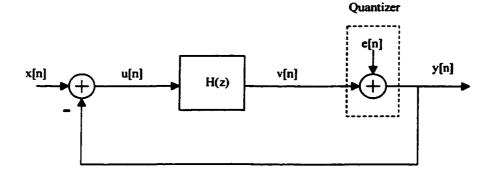

A general noise-shaped sigma-delta ( $\Sigma\Delta$ ) modulator is shown in Figure 2.4 [32]. This structure is known as an interpolative structure and is analogous to an amplifier realized using an opamp and feedback. In this structure, the feedback reduces the effect of the noise of the output stage of the opamp in the closed-loop amplifier's output signal at low frequencies when the opamp gain is high. At high frequencies, when the opamp's gain is low, the noise is not reduced.

The signal transfer function STF(z) and the noise transfer function NTF(z) are:

$$STF(z) = \frac{Y(z)}{U(z)} = \frac{H(z)}{1 + H(z)}$$

(2.8)

$$NTF(z) = \frac{Y(z)}{E(z)} = \frac{1}{1 + H(z)}$$

(2.9)

The zeros of the noise transfer function will be equal to the poles of H(z). When H(z) goes to infinity, NTF(z) will go to zero.

If we choose H(z) such that its magnitude is large from 0 to  $f_B$  (i.e., over the frequency band of interest), we can noise-shape the quantization noise in a useful manner. With such a choice, the signal transfer function will approximate unity over the frequency band of interest very similarly to an opamp in a unity-gain feedback configuration [32]. Furthermore, the noise transfer function NTF(z)

Figure 2.4 The linear model of the modulator

will approximate zero over the same band. Thus the quantization noise is reduced over the frequency band of interest while the signal itself is largely unaffected.

#### 2.2.3.3 First Order Sigma-delta Modulator

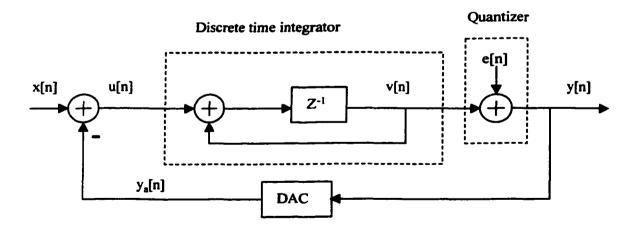

The diagram of the first-order  $\Sigma\Delta$  modulator is shown in Figure 2.5.

The modulator consists of an integrator, an internal ADC or quantizer, and a DAC used in the feedback path. It is easily shown that the output of the integrator is

$$v[i] = x[i-1] - e[i-1]$$

(2.10)

and the quantized signal is

$$y[i] = x[i-1] + (e[i] - e[i-1])$$

(2.11)

Thus this circuit differentiates the quantization error, making the modulation error the first difference of the quantization error while leaving the signal unchanged, except for a delay.

The DAC in the modulator is required to be nearly as linear as the overall conversion resolution. Any DAC nonlinearity can be modeled as an error source that adds directly to the input. This error source benefits from the oversampling but unlike e[n], which models the ADC quantization error, is

Figure 2.5 First order sigma-delta modulator

not subject to the noise shaping. I-bit DAC is frequently used in oversampling techniques. The advantage of 1-bit DAC is that it is inherently linear [32], it has only two output values, and since two points define a straight line, no trimming or calibration is required. This inherent linearity is one of the major motivations for making use of oversampling techniques with 1-bit converters. It is common to use a 1-bit DAC and a corresponding 1-bit quantizer, which is simply a comparator. Consequently, if the sampling frequency is high enough, the sigma-delta ADC allows the use of a 1-bit quantizer to achieve high overall resolution.

To calculate the effective resolution of the  $\Sigma\Delta$  modulator, we assume that the error *e* behaves as white noise that is uncorrelated with the input signal, the spectral density of the modulation noise

$$n_{i} = e_{i} - e_{i-1} \tag{2.12}$$

may then be expressed as

$$N(f) = E(f) \left| 1 - \varepsilon^{-j\omega T} \right| = 2e_{rms} \sqrt{T} \sin\left(\frac{\omega T}{2}\right)$$

(2.13)

where  $\omega = 2\pi f$ ,  $T = 1/f_s$ ,  $f_s$  is oversampling frequency.

In Figure 2.5, the feedback around the quantizer reduces the noise at low frequencies but increases it at high frequencies. The total noise power in the signal band is

$$P_n = \int_{f_B}^{f_B} |N(f)|^2 df \approx e_{rms}^2 \frac{\pi^2}{3} (2f_B T)^3 = e_{rms}^2 \frac{\pi^2}{3} \frac{1}{OSR^3} = \frac{\Delta^2 \pi^2}{36} \left(\frac{1}{OSR}\right)^3$$

(2.14)

where  $f_B$  is the signal band, and OSR is the oversampling ratio.

From equation.(2.5) and (2.14), we can calculate the maximum SNR as

$$SNR_{\max} = 10 \log\left(\frac{P_s}{P_{\pi}}\right) = 10 \log\left(\frac{3}{2}2^{2N}\right) + 10 \log\left(\frac{3}{\pi^2}(OSR)^3\right)$$

(2.15)

which is also equal to

$$SNR_{max} = 6.02N + 1.76 - 5.17 + 30\log(OSR)$$

(2.16)

Here we can see each doubling of the oversampling ratio of this circuit reduces the noise by 9 dB and provides 1.5 bits of extra resolution. The improvement in resolution requires that the modulated signal be decimated to the Nyquist rate with a sharply selective digital filter. Otherwise, the highfrequency components of the noise will spoil the resolution when it is sampled at the Nyquist rate.

#### 2.2.3.4 High Order ∑∆ Modulator

The objective of using  $\Sigma\Delta$  modulator is to reduce the net noise in the signal band. To do this well, we need to subtract from the quantization error a quantity whose in-band component is a good prediction of the in-band error. Ordinary  $\Sigma\Delta$  modulation subtracts the previous error. Higher order prediction should give better results than this first-order prediction.

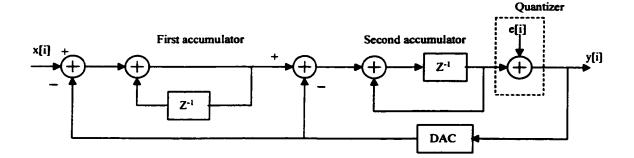

Figure 2.6 shows the second-order  $\Sigma\Delta$  modulator. It is an iteration of  $\Sigma\Delta$  feedback loops. The output of this modulator can be expressed as

$$y[i] = x[i-1] + (e[i] - 2e[i-1] + e[i-2])$$

(2.17)

So the modulation noise is now the second difference of the quantization error. The spectral density of this noise is

$$N(f) = E(f) \left(1 - \varepsilon^{-\gamma vT}\right)^2$$

(2.18)

and the noise power in the signal band is given by

Figure 2.6 Second-order  $\Sigma\Delta$  modulator

$$P_{n} = \int_{f_{B}}^{f_{B}} |N(f)|^{2} df \approx e_{rms}^{2} \frac{\pi^{4}}{5} (2f_{B}T)^{5} = e_{rms}^{2} \frac{\pi^{2}}{5} \frac{1}{OSR^{5}} = \frac{\Delta^{2}\pi^{4}}{60} \left(\frac{1}{OSR}\right)^{4}$$

(2.19)

From equation (2.5) and (2.19), we can calculate the maximum SNR as

$$SNR_{\max} = 10 \log\left(\frac{P_s}{P_n}\right) = 10 \log\left(\frac{3}{2}2^{2N}\right) + 10 \log\left(\frac{5}{\pi^4}(OSR)^5\right)$$

(2.20)

which is also equal to

$$SNR_{max} = 6.02N + 1.76 - 12.9 + 50 \log(OSR)$$

(2.21)

We can see that doubling the OSR improves the SNR for a second-order modulator by 15dB, or equivalently, a gain of 2.5 bits/octave.

If we use A as the amplitude of the encoded test signal,  $\Delta$  is the modulator output level. Then, the signal-to-noise ratio can also given by [9]

$$SNR = 15\log_2 OSR + 6\log_2 \left(\frac{A}{\Delta}\right) - 11.14, dB$$

(2.22)

We will use this equation later.

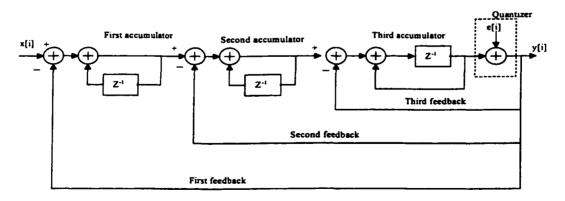

The technique can be extended to provide higher order predictions by adding more feedback loops to the circuit. Figure 2.7 shows the third-order  $\Sigma\Delta$  modulator, where DAC is not shown because 1-bit DAC is used.

Figure 2.7 Third-order  $\Sigma\Delta$  modulator

In this dissertation, the higher order  $\Sigma\Delta$  modulator is used for generating the high-resolution analog signal. Here is an example of the design of a 5<sup>th</sup> order sigma-delta modulator (Figure 2.8). In this example, all the zeros of the noise transfer function (NTF) are placed at z=1 (i.e. dc) so that the modulator could be used for various oversampling ratios. In other words, the zeros are not spread over the frequency band of interest, as that would restrict the modulator's usefulness to a particular oversampling ratio [32].

Since all the zeros are assumed to be at z=1, the NTF has the following form:

$$NTF = \frac{(z-1)^{5}}{D(z)} = \frac{(z-1)^{5}}{\prod_{i=1}^{5} (z-p_{i})}$$

(2.23)

Thus for a modulator of order 5, we have 5 degrees of freedom. To find the pole of the system, we need the modulator stability while shaping as much quantization noise away from dc as possible. Therefore a high-pass filter is obtained when poles are placed in a Butterworth configuration, so that the cutoff frequency of the Butterworth filter becomes the single degree of freedom [10]. Specifically, with a passband edge at fs/25, a 5<sup>th</sup>-order Butterworth high-pass filter has a peak gain equal to 1.34 (<=1.5 [12] [10] [13]), and the *NTF*(z) is given by

$$NTF = \frac{(z-1)^5}{z^5 - 4.4189z^4 + 7.8412z^3 - 6.9818z^2 + 3.1186z - 0.5589}$$

(2.24)

and

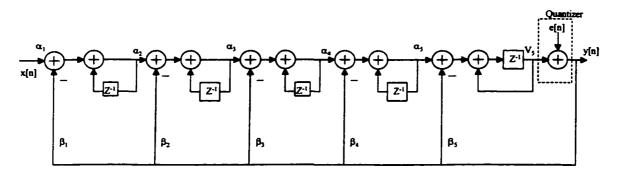

Figure 2.8 Cascade-of-integrators structure used to realize the 5<sup>th</sup>-order modulator

$$NTF = \frac{1}{1 + H(z)} \tag{2.25}$$

thus,

$$H(z) = \frac{1 - NTF(z)}{NTF(z)} = \frac{0.5808z^4 - 2.1577z^3 + 3.0170z^2 - 1.8812z + 0.4412}{(z-1)^5}$$

(2.26)

Next, a suitable implementation structure is chosen. In this example, a cascade-of-integrators structure is used, as shown in Figure 2.8.

The  $\alpha_i$  coefficients are set as  $\alpha_1=\beta_1$ ,  $\alpha_2=\alpha_3=\alpha_4=\alpha_5=1$ . By initially setting  $\alpha_1=\beta_1$ , we are allowing the input signal to have a power level similar to that of the feedback signal, y(n). In other words, if  $\alpha_1$ were initially set equal to one and  $\beta_1$  were quite small, then the circuit would initially be stable for only small input signal levels [32].

Coefficients  $\beta_i$  are found by deriving the transfer function from the 1-bit DAC output to the V<sub>5</sub> and equating that function to -H(z) in equation(2.26).

$$H(z) = \frac{z^4(\beta_1 + \beta_2 + \beta_3 + \beta_4 + \beta_5) - z^3(\beta_2 + 2\beta_3 + 3\beta_4 + 4\beta_5) + z^2(\beta_3 + 4\beta_4 + 6\beta_5) - z(\beta_4 + 4\beta_5) + \beta_5}{(z-1)^5}$$

(2.27)

Equating (2.27) with (2.26), the coefficients are found to be:

$$\alpha_1 = 0.0001, \ \alpha_2 = 1.0, \ \alpha_3 = 1.0, \ \alpha_4 = 1.0, \ \alpha_5 = 1.0$$

$\beta_1 = 0.0001, \ \beta_2 = 0.0025, \ \beta_3 = 0.0206, \ \beta_4 = 0.1164, \ \beta_5 = 0.4412$

As mentioned before, in the design of high order  $\Sigma\Delta$  modulator, stability needs to be considered. The choice of a Butterworth high pass configuration for the noise transfer function is due to the fact that the cutoff frequency of the Butterworth has some relation with the order of the modulator. In order to make the modulator stable: the higher the order of modulator, the lower the cutoff frequency. This means when we use a high order modulator to get higher in-band SNR, the cutoff frequency of Butterworth shifts left towards the origin point. Thus a higher order analog low pass filter (LPF) will be needed to follow the modulator in order to get a higher SNR. This will be detail discussed in detail in section 2.5.

#### 2.2.4 Parameter for the Performance of Bitstream: Length N

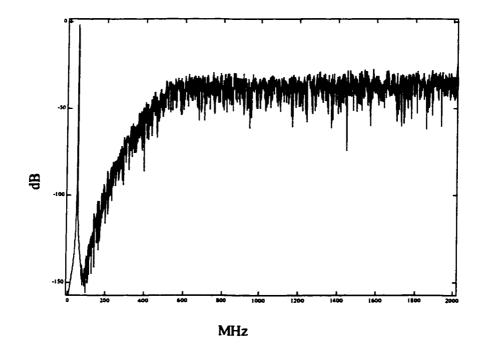

A  $\Sigma\Delta$  modulator is based on an infinite-impulse response system whose output maps the input signal into an infinite-long sequence of bits. As a result, with a periodic input such as a sinusoidal signal, the output signal does not repeat itself. This implies that there isn't a single sequence that we can extract from the modulator output and claim that it represents the input periodic signal. Fortunately, we can come close [6]. By ensuring that the input signal completes an integer number of cycles inside the PDM stream, the output bitstream when repeated will be a close approximation to the original PDM signal. This is accomplished by following the rules of Coherent sampling [15]. For the best approximation, one should also ensure that the N+1<sup>th</sup> bit of the sequence from which the N bits are being extracted is the same as the first bit of the pattern to avoid the most obvious discontinuity. Figure 2.9 shows the frequency response of a long bitstream, length is 2<sup>16</sup>. It is the output of  $\Sigma\Delta$ modulator. Figure 2.10 shows the frequency response of a short bitstream, length equals 2<sup>10</sup>. This short bitstream is part of the original long 2<sup>16</sup> one. From these two plots, we can see the short bitstream keeps the property of the long one: same noise shaping, but with decreased in-band SNR. The simulation shows the deterioration is about 1 to 2 bits by measuring in-band SNR and ENOB. As long as the resolution of the short bitstream is acceptable for the DUT, this method is fine.

According to the rules of Coherent sampling [15], an integer number of cycles of the test signal should be embedded in the pulse-density modulated (PDM) bitstream. This way, the test frequency  $f_i$  (analog input frequency for testing DUT) should be chosen as a submultiples of the sampling frequency  $f_i$ , which is

Figure 2.9 Frequency response of a long bitstream: length=2<sup>16</sup> (Matlab<sup>TM</sup> simulation result)

Figure 2.10 Frequency response of a short bitstream, length=2<sup>10</sup> (Matlab<sup>™</sup> simulation result)

$$f_t = \frac{M}{N} f_s, \qquad M = 1, 2, 3, ..., \frac{N}{2}$$

(2.28)

where N is the length of the bitstream.

From equation (2.28), we can see the test frequency  $f_r$  is an integer multiple of the primitive frequency,  $f_s/N$ . In other words, the test frequency should consist of only those frequencies that are harmonically related to the primitive frequency. This also suggests that the primitive frequency limits the frequency resolution of the signal generation scheme [6]. For a fixed sampling frequency  $f_s$ , the resolution can only be improved by increasing the sequence length N. Also, it is noted, to encode the test signal into a PDM stream, it is essential that the signal lie within the bandwidth of the  $\Sigma\Delta$ modulator, i.e.,

$$f_t \le f_B \tag{2.29}$$

According to equation (2.22), for the  $2^{nd}$  order  $\Sigma\Delta$  modulator, for a desired SNR, the bandwidth  $f_B$  of the  $\Sigma\Delta$  modulator can be expressed as

$$f_B = f_s \times 2^{\frac{1}{15} \left( SNR + 26 - 6 \log_2 \left( \frac{A}{\Delta} \right) \right)}$$

(2.30)

Substituting equation (2.28), and equation (2.30) into equation (2.29), we got,

$$\frac{M}{N}f_s \le f_s \times 2^{\frac{1}{15}\left(SNR+26-6\log_2\left(\frac{A}{\Delta}\right)\right)}$$

(2.31)

or, eliminating  $f_s$ , it can be written as

$$\frac{M}{N} \le 2^{\frac{1}{15}\left(SNR+26-6\log_2\left(\frac{A}{\Delta}\right)\right)}$$

(2.32)

From equation (2.32), we can see the basic relationship between the sequence length N, the test tone frequency index N, the signal quality denoted by SNR over the modulator bandwidth of  $f_B$ , the

amplitude of the encoded test signal A, and the modulator output level  $\Delta$ . Here we need to mention that the SNR value is over the modulator bandwidth  $f_B$ , so it is an ideal SNR value.

As an example, if a design has a shift register ring with length N=1024, running at a frequency of 500MHz, assuming the signal amplitude A is 1, the bitstream level is  $\pm 1$ , ( $\Delta$ =2), then according to equation (2.32), we got,

$$M \le 1024 * 2^{\frac{1}{15}(SNR+32)}$$

(2.33)

There is a trade-off between the number of available frequencies and their signal quality if the bitstream length is fixed. For instance, if 80dB is desired, then test frequencies corresponding to M less than 5.8 are possible. So, M can take on integer values between 1 and 5. The primitive frequency in this case is 500MHz/1024=0.488MHz. The corresponding test frequencies that can be generated using a 500MHz clock are 0.488MHz, 0.976MHz, 1.464MHz, 1.952MHz, 2.44MHz.

Also, from equation (2.33), we can find the minimum length of sequence that can meet the SNR quality requirement. By setting M=1 in equation (2.32), we got

$$N_{\min} = 2^{\frac{1}{15} \left( SNR + 26 - 6 \log_2 \left( \frac{A}{\Delta} \right) \right)}$$

(2.34)

Here we need to note that  $N_{min}$  is the ideal value, because the SNR value only counts the in-band noise power.

In this dissertation, we use this bitstream generation method to generate an on-chip analog signal. This analog signal will feed in the ADC, which is the device under test (DUT) (Figure 1.1). This DUT does not have frequency selectivity, and it will accept a much higher frequency range. Thus, the noise power needs to be counted to a much higher frequency range after the LPF to attenuate the high frequency noise. Consequently, the  $N_{min}$  will be higher than equation (2.34).

#### 2.2.5 Bitstream Optimization

Once a long sequence has been obtained, the best bitstream of length N in the sequence can be chosen. This can be accomplished through the use of different selection criteria [1]. These criteria include maximum spurious-free dynamic rage (SFDR), amplitude precision and maximum SNR. The optimization is based on a search, where different N-length bitstreams selected from y(n) are evaluated. This can be performed sequentially, moving the selection window bit by bit, or randomly, choosing a different bitstream every time. Both methods have similar results, but the random method usually converges to better results faster since closely spaced bitstreams in the sequence y(n) tend to have similar characteristics. The random method thus finds clusters of better bitstreams faster.

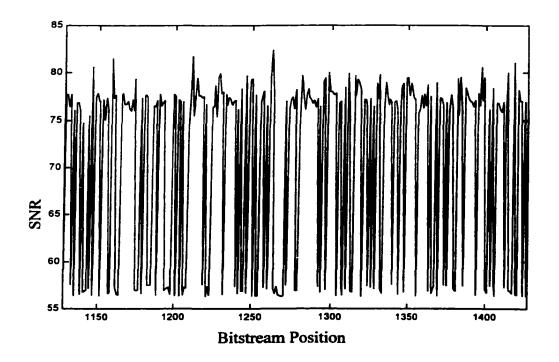

Figure 2.11 shows a plot of SNR versus the bitstream position. From the plot, we can see the SNR varies from 56dB to 81dB. The small variance of amplitude will have a similar effect, which may cause the SNR to have about a 20dB variance.

Simulation shows for a fixed length bitstream, the best bitstream will change the position if the amplitude is changing. But what will be kept is the SNR of the best bitstream. For amplitude  $A_{mp1}$ , there is a best bitstream in position  $P_1$ , which will generate  $SNR_1$ . For another amplitude  $A_{mp2}$ , there is another best bitstream in position  $P_2$ , which will generate  $SNR_2$ . Simulations show as long as the original long bitstream length is fixed, and using the same order sigma-delta modulator, these two SNR values:  $SNR_1$  and  $SNR_2$  will have a similar value. This means, in the best bitstream search, we do not need to perform double loop search: position and amplitude. One loop search is enough.

After bitstream optimization, the accuracy of analog signal encoded in the bitstream can achieve the best result.

Figure 2.11 SNR vs. bitstream position

# 2.3 Shift Register Ring

Now we have the bitstream which is generated from the software, i.e. Matlab<sup>TM</sup> (Figure 1.1). We need to store this bitstream. The shift register is used here to store the bitstream and also to repeat the bitstream. If we use a signal source to provide a sinewave for the tester, we would have the signal source always ON during the test. Similarly here, we want the bitstream always provided for the DUT, so we use the shift register to repeat the bitstream. It works like a signal source which is always running. The length of the shift register will be N, which is also the length of bitstream. The operating frequency of the shift register ring will be the frequency of the oversampling  $\Sigma\Delta$  modulator. For example, if the analog input signal for testing is 1.46434875MHz (this frequency will be explained

soon), the oversampling frequency  $f_{s}$  is 500MHz, which means the oversampling ratio is 1024/3, then the shift register ring should operate at 500MHz. This also sets a limit on the software, which means even in the software, the oversampling ratio has a limit.

The bitstream length N will be decided by the size of the shift register on the chip. Within N bitstream, there will includes M complete cycles, as we discussed before, to follow the Coherent sampling rule, and this N and M need to be relatively prime numbers. In the example above, the N is 1024, M is 3, (We want 3 cycles in the bitstream stored on chip). According to equation (2.28),

$$f_t = \frac{3}{1024} \times 500 MHz = 1.46434875 MHz$$

# 2.4 1-bit DAC

The output of shift register ring (Figure 1.1) is a repeated bitstream. The bitstream then goes through a 1-bit DAC to generate 1-bit analog signal. This 1-bit DAC makes the transition from the digital codes (one or zero) to the analog domain (Vdd or Vss,  $V_{DAC}^+$  or  $V_{DAC}^-$ , etc.). It acts as a buffer between the digital logic and the analog filter. This 1-bit DAC also need to work at the same speed as the shift register.

# 2.5 Analog Low Pass Filter

### 2.5.1 Specification of LPF

As mentioned earlier, the bitstream is noise shaped, with noise at the high frequency range. The output of the 1-bit DAC still has the same noise shaping: noise at the high frequency range. Therefore an analog low pass filter is needed to filter out the high frequency noise in order to get the high quality analog signal that is encoded in the bitstream by the  $\Sigma\Delta$  modulator.

The choice of analog low pass filter is guided by the chosen NTF (noise transfer function) of the sigma-delta modulator and the attenuation of the out-of-band noise needed. Since we have chosen the high pass Butterworth configuration for the noise transfer function, a low pass Butterworth filter is chosen for filtering out the high frequency noise.

As mentioned earlier, for a high order  $\Sigma\Delta$  modulator, its high SNR depends on the following LPF to attenuate the out-of-band noise (Figure 1.1).

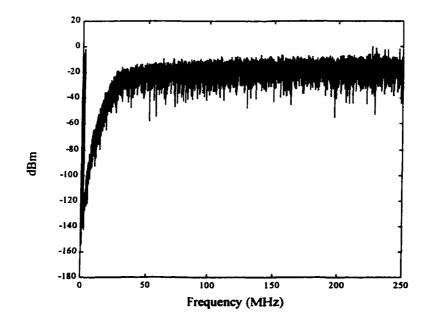

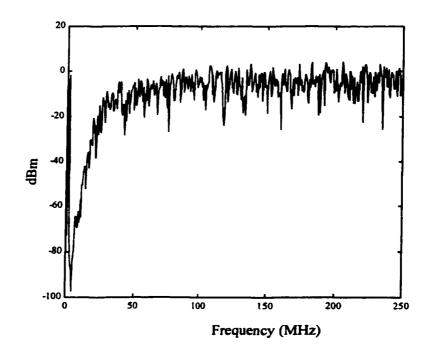

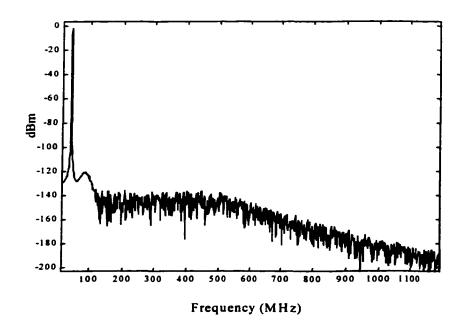

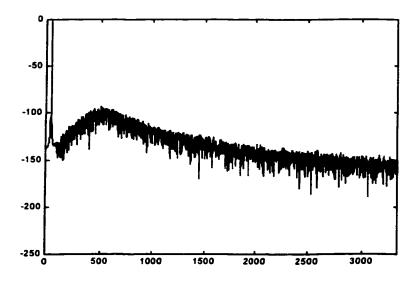

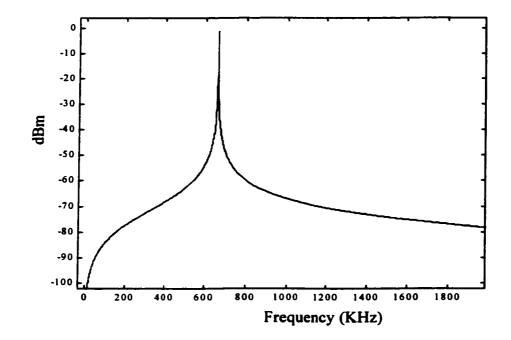

Figure 2.12 shows a 7<sup>th</sup> order sigma-delta modulator frequency response. Figure 2.13 shows the frequency response of this 7<sup>th</sup> order modulator followed by a 7<sup>th</sup> order LPF. The resulting SNR is 98.1132dB. Figure 2.14 shows the same modulator followed by a 4<sup>th</sup> order LPF. The resulting SNR is 75.8411dB. Figure 2.15 shows the modulator followed by a 2<sup>nd</sup> order LPF, SNR=43.0123dB.

From the above three comparisons, we can see clearly that the performance of the analog signal generated on chip depends on the analog LPF chosen following the modulator. Generally speaking,

Figure 2.12 7th order sigma-delta modulator frequency response

Figure 2.13 7<sup>th</sup> order modulator followed by 7<sup>th</sup> order Butterworth LPF, SNR=98.1132dB, ENOB=16.0055

Figure 2.14 7<sup>th</sup> order modulator plus 4<sup>th</sup> order LPF, SNR=75.8411dB, ENOB=12.3058

Figure 2.15 The same modulator followed by a 2<sup>nd</sup> order modulator, SNR=43.0123, ENOB=6.8525

From the above three comparisons, we can see clearly that the performance of the analog signal generated on chip depends on the analog LPF chosen following the modulator. Generally speaking, the order of the analog LPF should preferably be one order higher than the loop-filter order of the sigma-delta modulator, to suppress the high-frequency noise [16]. Otherwise, the analog signal generated will be affected by the nonlinearity of the LPF.

What we need to note is that the above SNR calculation counts the noise power through the entire Nyquist frequency band, not only the in-band SNR as calculated in equations (2.16) and (2.21). The SNR here is lower than in those equations. Since at this point, we do not know what the device under test (DUT) is, we do not know if it has frequency selection or saying limited bandwidth, so we need to account for all the Nyquist frequency range noise power.

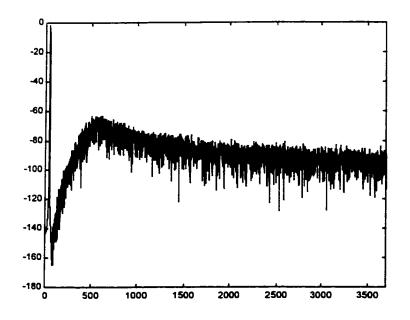

Figure 2.16 shows the 7<sup>th</sup> order vs. 2<sup>nd</sup> order modulators. From this figure, we can see that higher order modulators need high order LPFs to attenuate out-of-band noise. The noise floor of the lower order modulator is relatively flat in low the frequency range compared with the higher order modulator. For our design, the goal is to test a 9-bit ADC. An analog signal with 11bit accuracy is needed for the test. Considering the random noise in the 1-bit DAC and the analog LPF that further deteriorate the signal's quality, a 12-bit accuracy signal is needed from the modulator that is software generated. Thus, a 4<sup>th</sup> order Butterworth LPF is needed (Figure 2.14)

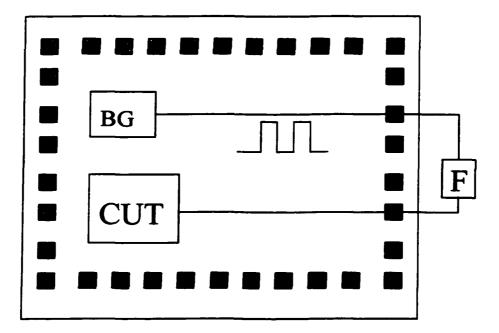

For a practical system, the LPF can reside off or on chip. As shown in Figure 2.17, BG is the bitstream generator, F is the filter, and CUT is the circuit under test. While an off-chip LPF has some limitations as a BIST method, it has merits for calibration and characterization [1]. First, it gives full flexibility in the passband choice of for the filter, extending the ranges of signals that can be generated. Second, the filter can be tuned to optimize its performance. The drawback is the use of two pins for the filter and the deteriorating performance and design complexity due to the pin and package parasitics for those pins.

Figure 2.16 7th order vs. 2nd order modulator frequency response

### 2.5.2 Power Consideration of the Generated Analog Signal

If the LPF is ideal, the generated analog signal power at its output will be the same as the input signal power of the modulator, which is implemented by software (Figure 1.1).

Let the amplitude of analog input signal of the modulator be  $A_m$ , the digital levels for the modulator output code y[n] be 1 and 0. The 1-bit DAC, which follows the LPF, has two voltage levels:  $V_{DAC}^+$  and  $V_{DAC}^-$ . In this design, using TSMC's 0.25µm process,  $V_{DAC}^+$  will be  $V_{ref}^+$ , and  $V_{DAC}^-$  will be the input range of the analog LPF. The power of the analog input signal  $A_m \sin \omega t$  of the modulator is then

$$P_{S_{-}IN} = \frac{1}{2}A_{m}^{2}$$

(2.35)

Figure 2.17 Filter off-chip scheme

and the average power for the output code y[n] (for code level 0 or 1) is

$$P_{TOT} = \frac{1}{M} \sum_{i=1}^{i=M} y^2[i] = \frac{1}{2}.$$

(2.36)

The average power for the output of the 1-bit DAC is

$$P_{TOT,DAC} = \frac{1}{M} \sum_{i=1}^{i=M} y_{DAC}^2 [i] = \frac{1}{2} (\Delta V_{DAC})^2 = \frac{1}{2} \Delta V_{DAC}^2$$

(2.37)

where  $\Delta V_{DAC} = V_{DAC}^+ - V_{DAC}^-$ . This is shown in Figure 2.18. And we also can see

$$P_{TOT,DAC} = P_{dc} + P_S + P_N \tag{2.38}$$

Where  $P_{dc}$  is dc power,  $P_S$  is the signal power at the output of the LPF, and  $P_N$  is the output allband noise power. They are:

Figure 2.18 Power for the input and output of the  $\Sigma\Delta$  modulator ( $\omega_x$  is the analog testing signal generated by the  $\Sigma\Delta$  modulator)

$$P_{dc} = \left(\frac{1}{2}\Delta V_{DAC}\right)^2 = \frac{1}{4}\Delta V_{DAC}^2$$

(2.39)

$$P_{S} = \left(\frac{1}{2}A_{m}\right)^{2} = \frac{1}{4}A_{m}^{2}$$

(2.40)

$$P_{N} = \frac{1}{4} \Delta V_{ref}^{2} - \frac{1}{4} A_{m}^{2}$$

(2.41)

After the analog LPF, if it is ideal, we will get the signal power, which is Ps in equation (2.40). The reason that  $P_s = \frac{1}{2} P_{s_{-IN}}$  is the output code of the modulator is two levels: 1 and 0. If the code levels are +1 and -1, we will get  $P_s = P_{s_{-IN}}$ . In this dissertation, we use the code levels +1 and -1.

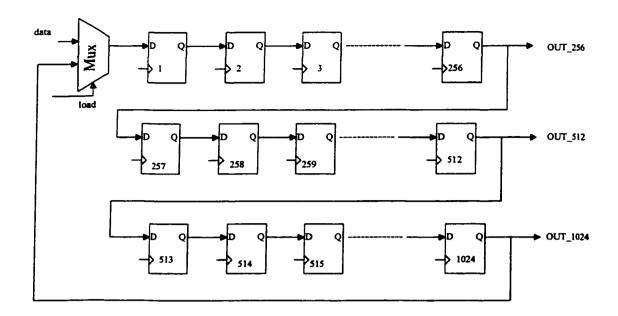

# 2.6 Multi-phase Signal Generation

The shift register ring also has the capability of providing a multi-phase signal [6]. By tapping off selected locations in the chain, one can obtain signals phase-shifted from the original to a resolution of 360/K degrees, where K is the shift register length N divided by the number of cycles in the bitstream,

$$K = \frac{bitstream length N}{\# of cycles}$$

(2.42)

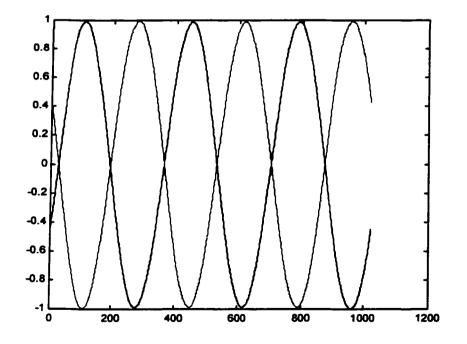

For example, if the bitstream length N is 1024, and it contains a 2-cycle sinewave, by driving outputs with the 256<sup>th</sup> and 512<sup>th</sup> flip-flops, we can get two output sinusoidal signals with  $\pi$  phase shift. These kinds of signals will be needed in the design if the DUT is fully differential. The diagram of multi-phase signal generation is shown in Figure 2.19, and generated two-phase signals are shown in Figure 2.20.

The schematics of the D-flip flops and a discussion of their operations can be found in section 6.3.

Figure 2.19 Diagram of multi-phase signal generation.

Figure 2.20 Generated multi-phase signals

# 2.7 Chapter Conclusion

In this chapter, the on-chip analog signal generation was discussed. It has been shown how a periodic signal that is encoded in an infinitely long PDM (pulse density modulated) bitstream can be very well approximated by a short-length periodic sequence of bits. It was also shown how to use memory on-chip to store the analog signal on chip. By using  $\Sigma\Delta$  modulator, a PDM bitstream is generated and stored and repeated by shift register ring. An analog LPF following shift register ring attenuates the high frequency range noise. Thus the on-chip analog signal is generated. With the on-chip analog signal generated, we can use it as an exciting signal for the device we want to test, which is the pipeline ADC in this dissertation.

# **3 ADC TESTING**

# **3.1 Introduction**

ADC testing is an important topic in this dissertation. As will be shown later, the re-configurable pipeline ADC architecture is based on its performance, in other words, the ADC testing results. In this chapter, the basic techniques of ADC testing will be carried out. It is composed of two parts: static testing and dynamic testing. The goal is to provide theoretical background to ADC testing.

First the quantization error in the ADC is analyzed. Then the techniques of Coherent sampling and histogram testing method are covered. Some examples are given for static and dynamic testings.

# **3.2 Error Measurements**

A key consideration in converter testing is that an ADC is not the mathematical inverse of a DAC [15]. An ideal DAC has no transfer ambiguity, but an ADC cannot be described by a point-to-point

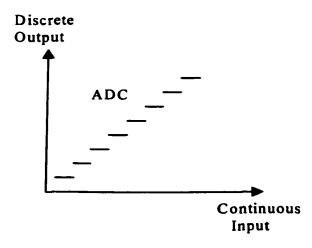

Figure 3.1 ADC transfer curve

map. An ideal ADC has a discrete output set, for each code out, there is a fuzzy input: a continuum of input voltage. This means an ADC has one-way uncertainty. If a specified analog level is applied to the input of a perfect ADC, we know precisely what its output code response will be. But if we are told, instead, only what the output code state is, we cannot tell the exact input voltage, only its range, as shown in Figure 3.1. The uncertainty is uniformly distributed over the width of the step, or the least significant bit (LSB), or the quantum size. It is a tenet of ADC testing that one does not test an ADC by applying DC voltages (or steps) and looking to see if the ADC responds with the right or wrong codes [15].

It is clear that we can identify and correct for all of the contributing factors: gain, offset, phase, and noise, by looking at the full collection of ADC codes in context (i.e., by analyzing the set as a vector not as isolated code words). ADC testing involves much statistical work.

### 3.2.1 Quantization Errors

The quantization process introduces an irreversible error. The quantization step is determined by the number of steps a signal is quantized into. This number of quantization steps is expressed in a number of (binary-weighted) bits N. A signal  $A_j + \varepsilon$  is ideally quantized into level  $A_j$  as long as the value of  $\varepsilon$  is between  $-\frac{q_s}{2} < \varepsilon < \frac{q_s}{2}$ , where  $q_s$  is the quantization level spacing, i.e. LSB (least significant bit). Quantization error basically never exceeds an amplitude level equal to  $\pm \frac{q_s}{2}$ . Signals

that are somewhat larger than  $A_{j} + \frac{q_{s}}{2}$  are quantized to the next quantization level  $A_{j+1}$ .

The mean-square-error due to quantization can be calculated. Aassume over a long period of time all levels of uncertainty within the quantizing region  $A_{j} + \frac{q_{s}}{2}$  appear the same numbers of times. A uniform probability density function over the interval  $-\frac{q_s}{2}$  to  $+\frac{q_s}{2}$  is defined as follows. The

mean-squared value of  $\boldsymbol{\epsilon}$  will be

$$E(\varepsilon^2) = \frac{1}{q_s} \int_{\frac{q_s}{2}}^{\frac{q_s}{2}} \varepsilon^2 d\varepsilon$$

(3.1)

The symbol E(.) represents the statistical expectation. The rms quantization error voltage can be represented by:

$$e_{rms}^2 = E(\varepsilon^2) = \frac{1}{12}q_s^2$$

(3.2)

or the RMS quantization distortion voltage is

$$D = \frac{q_s}{\sqrt{12}} \text{ volts, RMS}$$

(3.3)

In an N-bit linear binary ADC, there are  $2^{N}$  code levels in the full-scale range (FSR). The two end steps have no outer bounds, and so do not actually have statistical centers.

The RMS amplitude is

FS Sine Amplitude =

$$\frac{q_s \times 2^N}{\sqrt{8}}$$

volts, RMS (3.4)

The signal-to-noise ratio (SNR) can be calculated using equation (3.4) divided by the equation (3.3), resulting in:

$$SNR = 2^N \sqrt{1.5} \tag{3.5}$$

and expressing this in dB, results in:

$$SNR = N \times 6.02 + 1.76 \quad dB$$

(3.6)

It is sometimes convenient to compare the actual, in-circuit performance of converters by equating the distortion and/or noise with an ideal converter with fewer bits. The equivalent number of bits based on distortion or noise is given by solving the above equation for N:

$$ENOB = \frac{SNR - 1.76}{6.02}$$

(3.7)

## 3.3 Coherent Sampling [15]

The trivial case of coherence is the condition where everything runs at the same rate (i.e., where all ratios are 1:1). As the term implies, coherence means the condition in which every element is allowed to run at a different rate, if required, yet be completely time coordinated in any way the programmer chooses.

Here is an example, F1 is the sampling rate of an ADC under test. Say, 50Ms/s. We want to test this converter near Nyquist frequency. Now we want to find the test frequency F2. Coherent sampling determines the relation between F1 and F2 in this way:

$$F2 = F1 * M/N \tag{3.8}$$

where M and N are two relatively prime integers. If we choose N=1024, then a value of 511 is suitable for M, giving a test frequency F1=50\*511/1024=24.951172MHz.

In digital signal processing (DSP)-based testing, N equals to the number of samples, and M equals to the number of signal cycles. The amount of information available from a sampled waveform is maximized when M and N are relatively prime. With relatively prime ratios, the amount of information is proportional to N and is independent of M. A prime M/N ratio ensures that each cycle contributes unique, independent information.

Figure 3.2 and Figure 3.3 show the spectrum of a 6-bit ADC by choosing different M/N ratios, where in Figure 3.2 M and N are not relatively prime numbers and in Figure 3.3 M and N are relatively prime numbers. We can see the noise floor is different between these two plots. In this dissertation, we always follow the rule of Coherent sampling.

Figure 3.2 Spectrum of ideal 6bit ADC with N=1024, M=24, where noise floor is not correct

Figure 3.3 Spectrum of ideal 6bit ADC with N=1024, M=23

## 3.4 Linear Histogram Testing

The word "histogram" means a drawing or record of the past. In ADC testing, a histogram shows how many times each different output code word appears in the response vector, without regard to the location. The complete list is derived from the ADC output vector by a single TALLY instruction [15].

The analog input can be any wave whose amplitude distribution is known. However a linear ramp simplifies the computation because step width is directly proportional to the tally of each code. DNL is quickly obtained by subtracting the average step size. Ramp amplitude is not critical but is usually made a little larger than the nominal ADC range to allow for unit-to-unit variation in analog gain.

If there is an 8-bit ADC, containing 2048 data, there is totally 256 unique codes. We need to count the hits in each code or say step, like hit (1) counting how many times code level 1 appears, and hit(2) counting how many times code level 2 appears. The hit(0) and hit(255) are discarded, because these two steps have no outer bound. Also we need to count the average hit, which is (total hits)/(256-2). DNL is calculated by

$$DNL(i) = \frac{hit(i) - hit \_avg}{hit \_avg}$$

(3.9)

where *hit \_avg* is average hit.

And INL is calculated by

$$INL(i) = INL(i-1) + \frac{DNL(i) + DNL(i-1)}{2}$$

(3.10)

It is noted that the histogram method is blind to nonmonotonicity. It is also noted that the histogram method does pick up missing code, wherever the DNL = -1LSB.

Figure 3.4 The INL of an 8-bit ADC

Even in a so-called static test, linearity is a function of more than the DC decision levels. Inequality of step widths is partly caused by comparator noise, which randomly displaces the instantaneous decision levels. Use of a slower ramp can increase the tally resolution.

Figure 3.4 and Figure 3.5 show the typical INL and DNL plot of an 8-bit pipeline ADC. Since no DNL is equal to -1LSB, there are no missing codes.

code

Figure 3.5 The DNL of a 8-bit ADC

### 3.5 Dynamic Histogram Testing

The ADC response spectrum is easily obtained from the ADC output vector by the Fast Fourier transform (FFT). Figure 3.6 shows the spectrum from a single "tone", or pure sinusoid, at the frequency  $F_r = 43/1024 * Fs = 43/1024 * 50 MHz = 2.099609375 MHz$ . The physical frequency is usually the sampling rate, Fs, which is 50MHz. The absolute frequency is not critical in most cases, but the ratio is. If the input has to be exact in absolute frequency, then it would be Ft, not Fs. That becomes the physical standard. The critical thing is not to end up with a fraction of a test cycle left over. This is ideal for Coherent DSP techniques. For example, the Fs we chose here is 49.999872MHz, and Ft is 2.099604MHz.

From the dynamic test, especially when an FFT plot is available, the signal to noise ratio (SNR) and the Spurious-free dynamic range (SFDR) can be calculated. SFDR is defined to be the difference between the fundamental signal power and the highest harmonic power, which can be observed from the FFT plot. The SNR is defined to be the signal to noise power ratio, which can also calculated from the FFT result.

Figure 3.6 Spectrum of 6-bit ADC obtained with relatively prime M

# **3.6 Chapter Conclusion**

In this chapter, the background knowledge of ADC testing is addressed. The Coherent sampling concept is introduced. The histogram testing methods for both static testing and dynamic testing are covered. The goal is to provide theoretical background to ADC testing, which is important in this dissertation because the re-configuration pipeline ADC architecture is based on its dynamic performance measurement results. This will be shown in chapter 5.

# **4 ON-CHIP DYNAMIC TESTING OF ADCs**

# **4.1 Introduction**

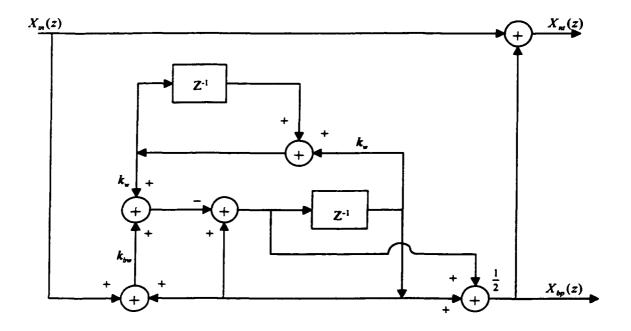

As we know, the key problem to be solved in BIST for pipeline ADCs is the on-chip measurement of SNR performance of the ADCs. The standard method in industry is the Fast Fourier Transform (FFT) method. Another alternative method, which will be used in this dissertation, is the Narrowband filter method [18]. In this chapter, these two methods of dynamic testing of pipeline ADCs are discussed. The emphasis is on the second method: a digital narrow band filter (NBF) method. The comparison of the two methods is covered based on the measuring accuracy and the complexity of the hardware implementation.

## **4.2 SNR**

### 4.2.1 FFT Method

Assume that in the frequency band of interest, the on-chip analog test stimulus is of the form

$$x_{in}(t) = A_x \cos(\omega_x t + \phi_x). \tag{4.1}$$

Let the ADC output be

$$y_{out}(n) = s(n) + \eta(t) \tag{4.2}$$

where s(n) is the signal and  $\eta(n)$  is the noise.

For optimum accuracy, a sample record  $y_{out}(n)$  consisting of M samples must contain an integer number of whole cycles of the sinewave [15]. To compute the SNR, first calculate  $Y_{out}(k)$ , which is the M-point DFT (Discrete Fourier Transform) of  $y_{out}(n)$  and is given by

$$Y_{out}(k) = \sum_{n=0}^{M-1} y_{out}(n) e^{-j(2\pi/M)kn}$$

(4.3)

Let the desired frequency component  $\omega_x$  be the j-th element of  $Y_{out}(k)$ . Based on Parseval's relation for the FFT, together with classical statistical theory [24], an estimate of the variance of the signal s(n), which is also the signal power  $\hat{P}_s$ , is given by

$$\hat{\sigma}_{s}^{2} = \hat{P}_{s} = \frac{2}{(M-1)M} |Y(j)|^{2}$$

(4.4)

An unbiased estimate of the noise power is given

$$\hat{\sigma}_{\eta}^{2} = \hat{P}_{\eta} = \frac{2}{(M-1)M} \sum_{k=1}^{(M-1)/2} |Y(k)|^{2}, k \neq j$$

(4.5)

From equation (4.4) and (4.5), we can get SNR for the test frequency  $\omega_x$  as

$$SNR = 10 \log_{10} \left\{ \frac{|Y(j)|^2}{\sum_{k=1}^{(M-1)/2} |Y(k)|^2, k \neq j} \right\}$$

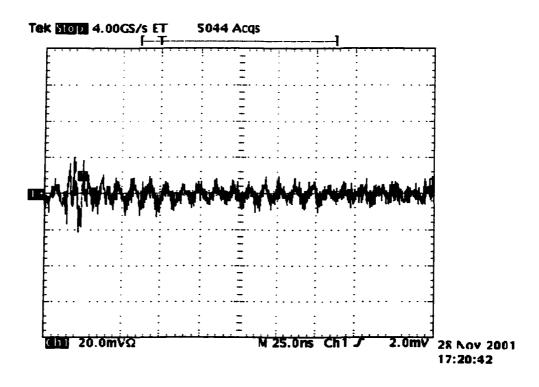

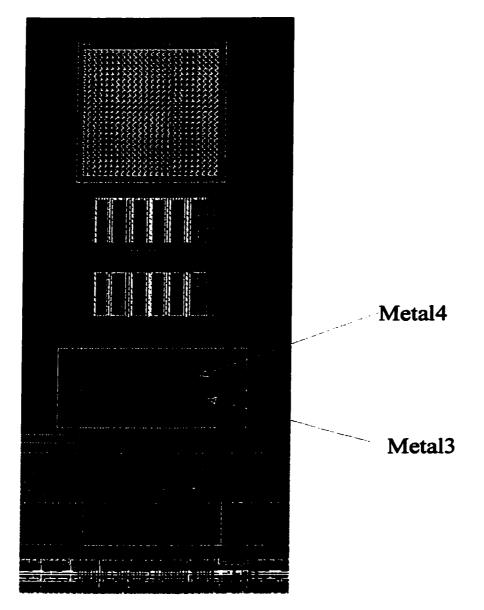

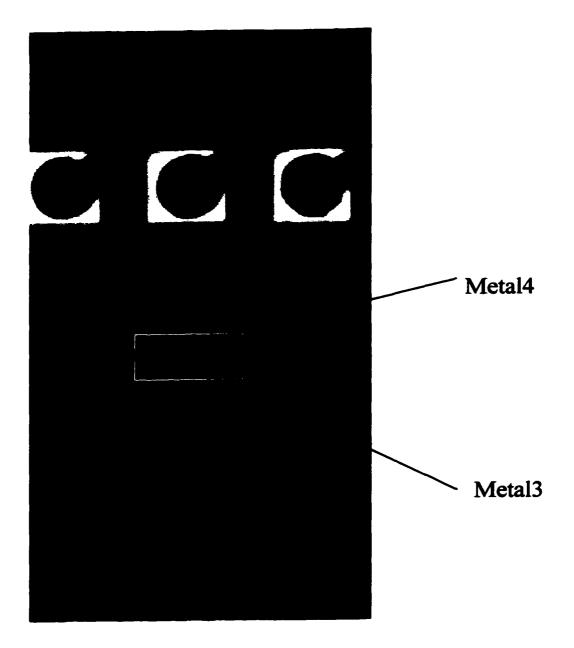

(4.6)